本篇目录:

- 1、互补输出结构的cmos门输出端是否可以并联使用?为什么?

- 2、推拉式TTL逻辑门输出端能否并联使用

- 3、门电路中哪些输出端可以并联使用

- 4、TTL门的输出可以并联使用吗?

- 5、将多个coms门的输入端、输出端并联时,能否提高电路的负载能力?

- 6、CMOS门电路两输入端分别接相同逻辑电平是时,输出端在并联使用可以...

互补输出结构的cmos门输出端是否可以并联使用?为什么?

1、不能 CMOS输出电阻很大,所以输出电平会受到负载电流的影响。

2、由于各个逻辑门的传输延时有差异,标准输出(推挽)的门电路一般不并联使用,集电极(漏极)开路输出的逻辑门可以并联使用。同一个芯片的逻辑门参数一致性好,估计问题不大,但是不建议这么做。

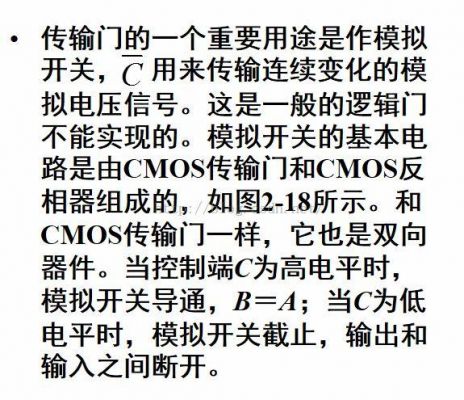

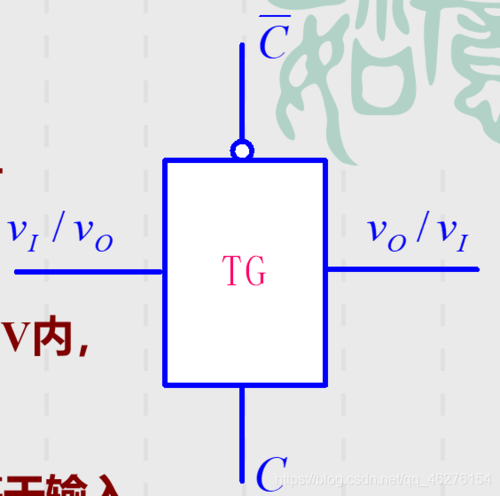

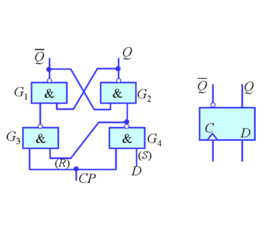

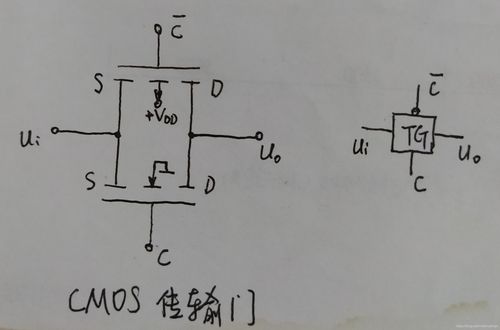

3、可以并联使用的门电路是CMOS的OD门、CMOS的三态门、CMOS传输门。用以实现基本逻辑运算和复合逻辑运算的单元电路称为门电路。常用的门电路在逻辑功能上有与门、或门、非门、与非门、或非门、与或非门、异或门等几种。

推拉式TTL逻辑门输出端能否并联使用

1、TTL集成电路输出端不允许并联使用(集电极开路(OC)与非门和三态(3S)输出门电路除外),否则不仅会使电路逻辑功能混乱,还会导致器件损坏。

2、除三态门、集电极开路门外,TTL集成电路的 输出端不允许并联使用,如果将几个集电极开路门电路的输出端并联,实现“线与”功能时,应在输出端 与电源之间接人上拉电阻。

3、TTL门电路输出端不允许并联使用 。TTL集成电路电源电压应满足SV +0. SV,电源接通瞬间及电路工作状态高速转换时,电源电流都会出现瞬态尖峰值,称为尖峰电流或浪涌电流,幅度可达4—5MA。

4、不管是TTL 还是CMOS,输出都不能直接连在一起,当一个输出高电平,另一个输出低电平,就会损坏输出电路。一般只允许输出接输入,因为输入的阻抗很高,不会损坏输出电路。

5、因为输出高电平的TTL门的上拉管会向输出低电平的门电路的下拉管灌大电流,导致过载可能损坏门电路。TTL电路采用双极型工艺制造,具有高速度和品种多等特点。 从六十年代开发成功第一代产品以来现有以下几代产品。

6、OC门可以并联,其他都存在烧毁的问题 但是实际上CMOS的门电路输出比较小,一般并联几个烧不掉的。

门电路中哪些输出端可以并联使用

答案:6。因为漏极开路门和集电极开路门有"线与"功能,输出可直接相与,故5正确,因为三态门通过使能控制有三种状态,故6正确。

只有OC门电路的输出可以并联使用,在外加上拉电阻后几个门电路的输出组成“线与”。

CMOS的OD门、CMOS的三态门、CMOS传输门。输出端需严格按照极性连接,否则不工作,可以并联使用的门电路是CMOS的OD门、CMOS的三态门、CMOS传输门。用以实现基本逻辑运算和复合逻辑运算的单元电路称为门电路。

A,OC门,集电极开路,可以输出级并联实现线与的功能。

TTL门的输出可以并联使用吗?

1、TTL门电路输出端不允许并联使用 。TTL集成电路电源电压应满足SV +0. SV,电源接通瞬间及电路工作状态高速转换时,电源电流都会出现瞬态尖峰值,称为尖峰电流或浪涌电流,幅度可达4—5MA。

2、不管是TTL 还是CMOS,输出都不能直接连在一起,当一个输出高电平,另一个输出低电平,就会损坏输出电路。一般只允许输出接输入,因为输入的阻抗很高,不会损坏输出电路。

3、不能直接并联,否则当并联输出端输出电平不一致时,输出高电平的TTL门的上拉管会向输出低电平的门电路的下拉管灌大电流,导致过载可能损坏门电路。

4、TTL集成电路输出端不允许并联使用(集电极开路(OC)与非门和三态(3S)输出门电路除外),否则不仅会使电路逻辑功能混乱,还会导致器件损坏。

将多个coms门的输入端、输出端并联时,能否提高电路的负载能力?

输出接全负反馈运放电路,相当于射极跟随器,提高输入阻抗降低输出阻抗。OPA340输出电压最大摆幅低于电源电压50mV,能够驱动低至600Ω负载。

由于各个逻辑门的传输延时有差异,标准输出(推挽)的门电路一般不并联使用,集电极(漏极)开路输出的逻辑门可以并联使用。同一个芯片的逻辑门参数一致性好,估计问题不大,但是不建议这么做。

不能 CMOS输出电阻很大,所以输出电平会受到负载电流的影响。

三态输出门可以用于串联电路,但不能直接用于并联电路,因为并联会产生竞争条件(即两个或多个输出信号同时驱动同一个输入线,导致电平不确定)。

CMOS门电路两输入端分别接相同逻辑电平是时,输出端在并联使用可以...

CMOS的OD门、CMOS的三态门、CMOS传输门。输出端需严格按照极性连接,否则不工作,可以并联使用的门电路是CMOS的OD门、CMOS的三态门、CMOS传输门。用以实现基本逻辑运算和复合逻辑运算的单元电路称为门电路。

如果是同一工艺下的mos管(管子特性几乎一致)是可以的。但如果是不同工艺的东西,比如说阈值电压不同,那么在多个cmos门的电流密度是不一样的。

除三态门、集电极开路门外,TTL集成电路的 输出端不允许并联使用,如果将几个集电极开路门电路的输出端并联,实现“线与”功能时,应在输出端 与电源之间接人上拉电阻。

不可以并联。由于转换速度不可能完全一致,有可能在状态转换瞬间出现一个输出端上导通,而另一个输出端下导通的情况。

不能 CMOS输出电阻很大,所以输出电平会受到负载电流的影响。

cmos集成门电路多余输入端可以并联,但一定要外接一个逻辑电平。

到此,以上就是小编对于传输门串联的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏