本篇目录:

- 1、为什么DDR4内存频率越高,PCB中地址线走线越长?

- 2、为什么大多数工程师喜欢用50欧姆作为PCB的传输线阻抗?

- 3、什么信号要布等长线?或什么情况下要画PCB布等长线?

- 4、PCB布线的常见规则?

- 5、PCB中多长的走线才是传输线

为什么DDR4内存频率越高,PCB中地址线走线越长?

相同容量条件下,内存频率越高,性能就越好。如果是不同代内存,比如DDR3和DDR4内存,如果是相同容量下,DDR4内存性能肯定在DDR3之上,毕竟DDR4内存频率均在DDR3之上,加之新一代内存还在带宽上有升级,功耗更低等。

内存频率 内存频率是DDR4和DDR5内存之间最直观的差别,DDR5相比DDR4内存在频率上实现了翻倍。DDR4上市初期,内存频率只有2133和2400MHz,目前主流频率为3200MHz和3600MHz,现阶段旗舰级DDR4内存频率可以做到4266MHz或更高。

今天小编将会为大家分享一下DDR4内存高低主频对电脑性能以及CPU、显卡、游戏性能的影响,相信大家从中可以找到想要的答案。

为什么大多数工程师喜欢用50欧姆作为PCB的传输线阻抗?

阻抗匹配的概念:阻抗匹配 主要用于传输线上,以此来达到所有高频的微波信号均能传递至负载点的目的,而且几乎不会有信号反射回来源点。

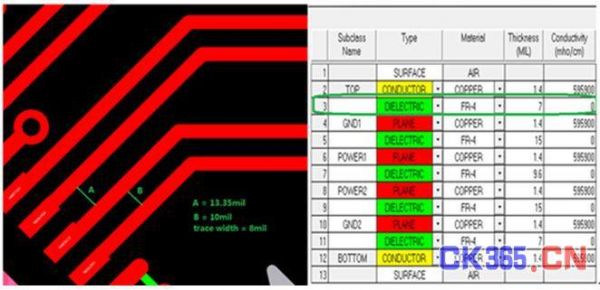

如果没有太多的阻抗线,可以把1到2层之间的厚度设厚点,这样天线就可以走粗点,具体要看你的PCB的密度已经有哪些信号线需要控阻抗的。一般1到2层的介质厚度9mil的话top层50欧姆走线线宽为6mil左右。

W原则一般是在50欧姆特征阻抗传输线条件下成立。PCB走线规则 3W规则:这里3W是线与线中心间距保持3倍线宽。你说3H也可以,但这里的H指的是线宽度,不是介质厚度。

调整传输线是加长源和负载间的距离,配合电容和电感把阻抗力调整为零。此时信号不会发生发射,能量都能被负载吸收。高速PCB布线中,一般把数字信号的走线阻抗设计为50欧姆。

什么信号要布等长线?或什么情况下要画PCB布等长线?

1、信号等长线和差分对不同,是为了读写信号或者某些相关信号需要同步才布等长线,这样信号不会出错。差分是为了达到阻抗要求而设置的。差分线上的信号需要阻抗匹配到一定值,否则制版后的测试信号是很差或者通不了。

2、确定PCB的层数电路板尺寸和布线层数需要在设计初期确定。如果设计要求使用高密度球栅数组(BGA)组件,就必须考虑这些器件布线所需要的最少布线层数。设计规则和限制自动布线工具本身并不知道应该做些什幺。

3、信号线布在电(地)层上 在多层印制板布线时,由于在信号线层没有布完的线剩下已经不多,再多加层数就会造成浪费也会给生产增加一定的工作量,成本也相应增加了,为解决这个矛盾,可以考虑在电(地)层上进行布线。

PCB布线的常见规则?

PCB布线时常见规则大概如下 信号完整性:保证信号的正确传输和抗干扰能力。这包括避免过长的信号线、适当的阻抗匹配和差分信号对的平衡等。 电源和地线:确保足够的电源和地线,并使用宽厚的铜层以降低电阻和电感。

初步划分数字、模拟、DAA电路在PCB板上的布线区域(一般比例2/1/1),数字、模拟元器件及其相应走线尽量远离并限定在各自的布线区域内。

PCB布线的基本规则1) 尽可能缩短信号线的长度。信号线长度越短,电阻和电感就越小,信号传输的速度也越快。2) 将信号线和电源线分开布线。信号线和电源线之间的干扰会导致噪声和杂波,影响信号的传输。

在 PCB 布线过程中,有几个重要的规则和技巧需要注意,以确保良好的电路性能和可靠性: 信号完整性:- 相关信号应尽可能短而直,以减少信号传输延迟和损耗。- 高速信号的差分对称性应得到保持,以减少串扰和噪声。

、PCB布线与布局隔离准则:强弱电流隔离、大小电压隔离,高低频率隔离、输入输出隔离、数字模拟隔离、输入输出隔离,分界标准为相差一个数量级。隔离方法包括:空间远离、地线隔开。

自动布线前,先用手工布一些重要的网络,比如高频时钟、主电源等,这些网络往往对走线距离、线宽、线间距、屏蔽等有特殊的要求;另外一些特殊封装,如BGA,自动布线很难布得有规则,也要用手工布线。

PCB中多长的走线才是传输线

1、越短越好。通常的模拟电路和数字电路中,百兆pcb走线的长度越短越好,比如电路中的信号线,走差分线,平行走线,可以防止外界的干扰和信号同步。

2、PCB布线的基本规则1) 尽可能缩短信号线的长度。信号线长度越短,电阻和电感就越小,信号传输的速度也越快。2) 将信号线和电源线分开布线。信号线和电源线之间的干扰会导致噪声和杂波,影响信号的传输。

3、Gbps pcb 走线等长要求确认同组线与线之间的间距要求,高速的DDR要求3W间距绕线的方式。常规走线线宽≥4mil(0.1016mm) (特殊情况可用5mil,即0.0889mm);小于这个值会极大挑战工厂生产能力,报废率提高。

4、针对上述传输线问题所引入的影响,我们从以下几方面谈谈控制这些影响的方法。1 严格控制关键网线的走线长度 如果设计中有高速跳变的边沿,就必须考虑到在PCB板上存在传输线效应的问题。

5、严格控制关键网线的走线长度 如果设计中有高速跳变的边沿,就必须考虑到在PCB板上存在传输线效应的问题。现在普遍使用的很高时钟频率的快速集成电路芯片更是存在这样的问题。

到此,以上就是小编对于pcb布线线间距的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏