本篇目录:

门电路详细解说与用途

1、如果有特殊要求,门电路当然也可以用pnp型晶体管作集电极开路输出,那样的话,当然就可以做到 “能够输出很大电流,而不能吸收很大电流”了。这样的用途比较少,所以,也比较少见。

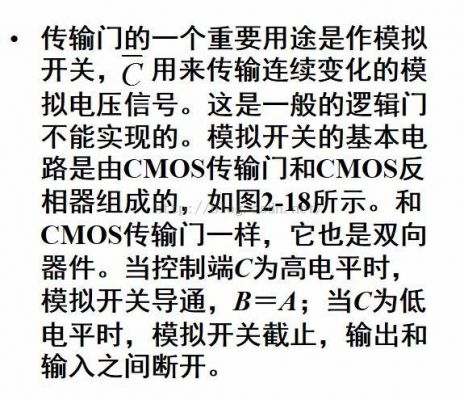

2、MOS电路具有制造工艺简单、功耗低、集成度高、电源电压使用范围宽、抗干扰能力强等优点,特别适用于大规模集成电路。

3、逻辑门可以用电阻、电容、二极管、三极管等分立原件构成,成为分立元件门。也可以将门电路的所有器件及连接导线制作在同一块半导体基片上,构成集成逻辑门电路。简单的逻辑门可由晶体管组成。

4、门电路的输入 用以实现基本逻辑运算和复合逻辑运算的单元电路称为门电路。常用的门电路在逻辑功能上有与门、或门、非门、与非门、或非门、与或非门、异或门等几种。

如何分析ttl电路

(1)输入全为高电平6V时。T2 、T3导通,VB1=0.7×3=1(V),T1的发射结因反偏而截止。此时T1的发射结反偏,而集电结正偏,称为倒置放大工作状态。由于T2导通,T3也饱和导通,输出电压为:Vo=Vces3≈0.3V。

【解答过程】:TTL集成门电路逻辑功能的分析①首先将TTL门电路划分为若干个图1中所示的基本功能结构模块。

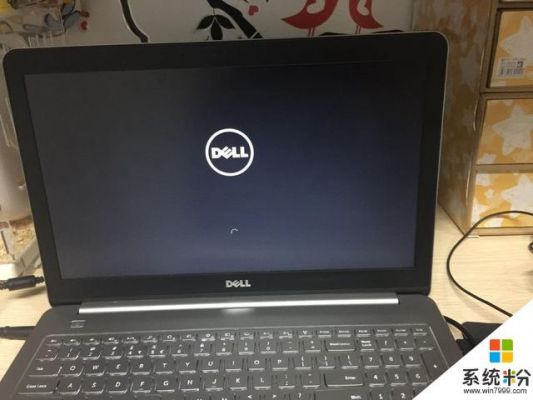

TTL电路输入电平判断10欧电阻接地是低电平输入;51kΩ电阻接地是高电平输入;悬空是高电平输入;输入电阻接地时,大于2kΩ(左右)时,是高电平输入,小于1kΩ左右是电平输入。1kΩ~2kΩ之间电平不确定。

TTL电路的基本环节是反相器。当输入高电平时, uI=6V,VT1处于倒置工作状态,集电结正偏,发射结反偏,uB1=0.7V×3=1V,VT2和VT4饱和,输出为低电平uO=0.3V。

集成度:一个封装内含有等效逻辑门的个数或元器件的个数。

逻辑门电路的详细介绍

逻辑门电路是数字电路中最基本的逻辑元件。所谓门就是一种开关,它能按照一定的条件去控制信号的通过或不通过。门电路的输入和输出之间存在一定的逻辑关系(因果关系),所以门电路又称为逻辑门电路。

基本逻辑门电路是组成数字电路的基础单元,实现各种复杂的逻辑功能。常见的逻辑门有与、或、非等类型。例如,CMOS非门、与非门、或非门、与门和或门都是基本的逻辑门电路。

与门(AND gate):与门是一个有两个或更多输入端和一个输出端的逻辑门电路。它的输出信号只有在所有输入信号同时为高(1)时才输出高(1),否则输出低(0)。与门可以用逻辑符号 ∧ 表示。

门电路详情介绍如下:定义:用以实现基本逻辑运算和复合逻辑运算的单元电路称为门电路。常用的门电路在逻辑功能上有与门、或门、非门、与非门、或非门、与或非门、异或门等几种。

ttl集成逻辑门的逻辑功能与参数测定

逻辑门是在集成电路(也称:集成电路)上的基本组件。逻辑功能:高、低电平可以分别代表逻辑上的“真”与“假”或二进制当中的1和0,从而实现逻辑运算。

与非门的逻辑功能是:当输入端中有一个或一个以上是低电平时,输出端为高电平;只有当输入端全部为高电平时,输出端才是低电平(即有“0”得“1”,全“1”得“0”。

做门电路实验时电源就是它的输入信号,接 为高电平、接-为低电平,悬空一般视为高电平。

【解答过程】:TTL集成门电路逻辑功能的分析①首先将TTL门电路划分为若干个图1中所示的基本功能结构模块。

“与”在逻辑运算中表示乘法。与非门的逻辑功能就是当输入端全是“1”时,输出为“0”。只要输入有一个是“0”,输出就为“1”。与非门的逻辑功能是与门和非门的叠加,有多个输入和一个输出。

到此,以上就是小编对于cmos传输门电路图的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏