本篇目录:

i2c中的fifo是异步的还是同步的

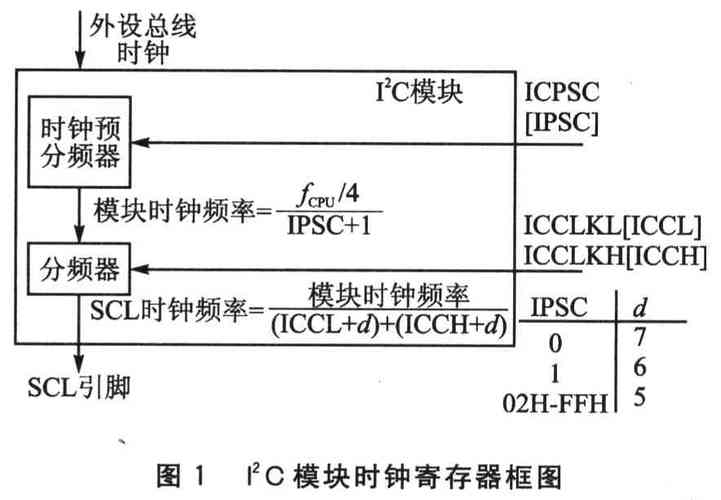

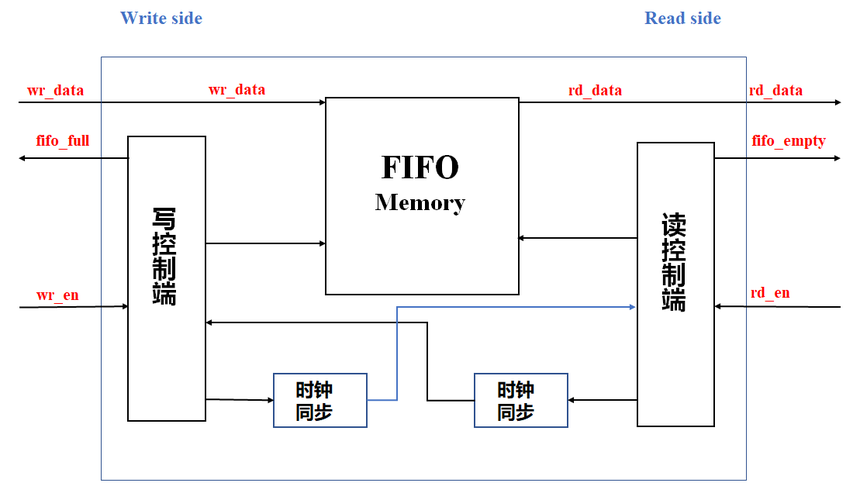

1、同步性 同步FIFO是其中相同的时钟用于读取和写入的FIFO。异步FIFO使用不同的时钟进行读取和写入,它们可能会引入亚稳定性问题。异步FIFO的常见实现方式是对读和写指针使用格雷码(或任何单位距离码),以确保可靠的标志生成。

2、这里的异步指的是不同频率/不同相位的时钟信号。而同步FIFO一般只用来作buffer。大概就是这样子。FIFO是不会实现数据位数的变换的。它只是实现了数据能被正确的传递。

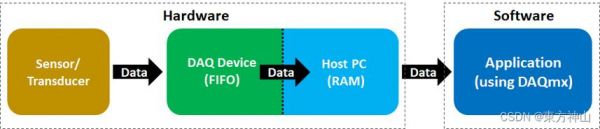

3、FIFO是First Input First Output的缩写,先入先出队列,这是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令。

异步FIFO的介绍

1、使用FIFO同步源自不同时钟域的数据是在数字IC设计中经常使用的方法,设计功能正确的FIFO会遇到很多问题,探讨了两种不同的异步FIFO的设计思路。两种思路都能够实现功能正确的FIFO。

2、同步FIFO是指读时钟和写时钟为同一个时钟在时钟沿来临时同时发生读写。异步FIFO读写时钟不一致,读写相互独立。异步FIFO最核心的部分就是精确产生空满标志位,这直接关系到设计的成败。

3、异步时钟的同步处理在数字电路中是很常见的,但也是很容易造成错误的地方,异步FIFO是进行同步化处理常用的手段之一。

4、这里的异步指的是不同频率/不同相位的时钟信号。而同步FIFO一般只用来作buffer。大概就是这样子。FIFO是不会实现数据位数的变换的。它只是实现了数据能被正确的传递。

5、对于异步FIFO而言,数据是由某一个时钟域的控制信号写入FIFO,而由另一个时钟域的控制信号将数据读出FIFO。也就是说,读写指针的变化动作是由不同的时钟产生的。因此,对FIFO空或满的判断是跨时钟域的。

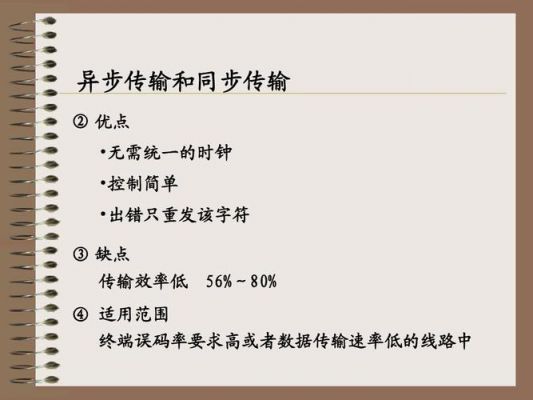

什么是同步电路?什么是异步电路?

同步电路:存储电路中所有触发器时钟输入接同一个时钟源,所有触发器的状态的变化与所加的时钟脉冲信号同步。

异步电路:主要是组合逻辑电路,用于产生地址译码器、FIFO或RAM的读写控制信号脉冲,但它同时也用在时序电路中,此时它没有统一的时钟,状态变化的时刻是不稳定的,通常输入信号只在电路处于稳定状态时才发生变化。

同步电路是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路,其所有操作都是在严格的时钟控制下完成的。这些时序电路共享同一个时钟CLK,而所有的状态变化都是在时钟的上升沿(或下降沿)完成的。

异步电路是指CLOCK之间没有倍数关系或者相互之间的相位关系不是固定的。异步电路无法作真正意义上的综合及STA,如果在同步电路里夹杂有异步电路。所以异步电路只有靠仿真来检查电路正确与否。

异步:所有触发器没有共用一个CP源,同步:优点,所有触发器的状态同时刷新,信号延迟时间短,缺点:结构复杂 异步:优点,结构简单,缺点,触发器状态刷新不同步,信号延迟可能会累积从而出现状态异常。

到此,以上就是小编对于异步传输模式优缺点的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏