本篇目录:

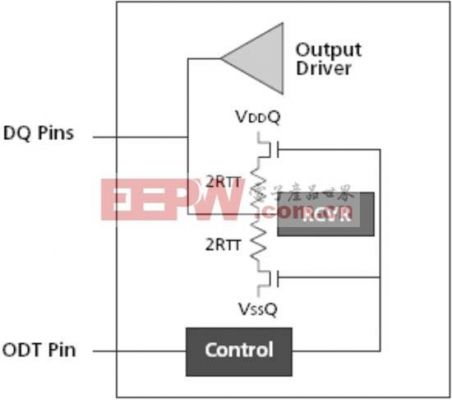

ddr的时钟为啥要下拉呢

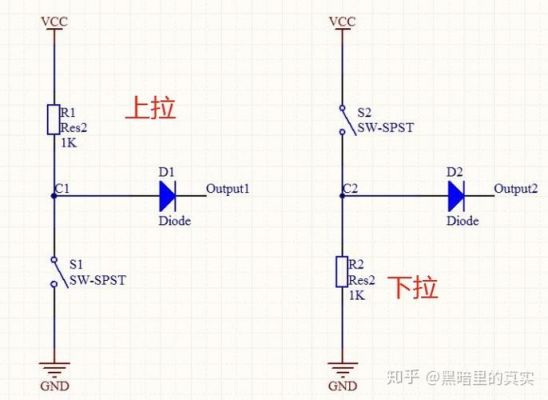

上拉,就是通过一个电阻将信号接电源,一般用于时钟信号数据信号等。下拉,就是通过一个电阻将信号接地,一般用于保护信号。这是根据电路需要设计的,主要目的是为了防止干扰,增加电路的稳定性。

因为DDR在时钟上升期和下降期都进行数据传输,其一个周期传输两次数据,相当于SDRAM频率的二倍。习惯上称呼的DDR频率是其等效频率,是在其实际工作频率上乘以2,就得到了等效频率。

换句话说,虽然DDR2和DDR一样,都采用了在时钟的上升延和下降延同时进行数据传输的基本方式,但 DDR2拥有两倍于DDR的预读取系统命令数据的能力。

DDR3内存通常值为90-120。低于80时,可能导致不稳定。CL、tRCD、tRP和tRAS称为第一时序,对颗粒性能的影响最明显,也最重要。

“真实时钟频率 267 MHz (DDR)”就是硬件运行的频率,而所谓的“有效时钟频率”是指等效于上一代的SDRAM(如PC133 SDRAM)运行的频率。上一代内存只是时钟的上升沿传输数据而已,下降沿不传输。

在DDR的PCB布线中提到,数据线可以分组等长,各组之间可以不等长,那怎样...

1、因为其不等长的原因,需要超过1个(事实上是数个,这个数字现在一般是5-8)钟频完成读、写等操作。数据调取给CPU的缓存也是类似等待的周期。由于引脚的并行排布,不需要担心数据的读取先后造成顺序错误。

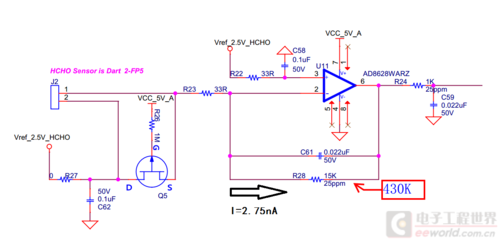

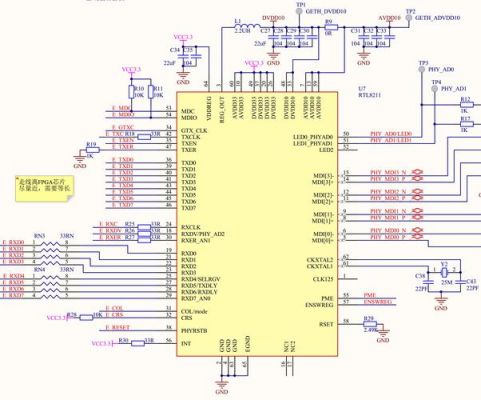

2、DDR的地址和控制信号线为一组,和DDR 的CLK的布线长度相差不超过400mil,信号线之间间隔10mil-15mil,宽度一般为5mil。

3、DDR之所以能实现双边沿触发,其实是在芯片内部做了时钟的倍频,对外看起来,数据地址速率和时钟一样。

ddr的工作原理详细解说

DDR SDRAM 在规格上按信号延迟时间(CL;CAS Latency,CL是指内存在收到讯号后,要等待多少个系统时钟周期后才进行读取的动作。一般而言是越短越好,不过这还要看内存颗粒的原始设定值,否则会造成系统的不稳定)也有所区别。

逻辑Bank数量DDR2SDRAM中有4Bank和8Bank的设计,目的就是为了应对未来大容量芯片的需求。而DDR3很可能将从2Gb容量起步,因此起始的逻辑Bank就是8个,另外还为未来的16个逻辑Bank做好了准备。

DDR内存的工作原理是通过在每个时钟周期中传送两次数据,即上升沿和下降沿都进行数据传输,这就使得DDR内存每秒钟能传输两倍于其工作频率的数据。

存储器讲述工作原理及作用 介绍 存储器(Memory)是现代信息技术中用于保存信息的记忆设备。

到此,以上就是小编对于ddr2端接电阻的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏