本篇目录:

如何正确使用FPGA的时钟资源

1、如果是系统时钟,就是主要用该时钟,则用全局时钟驱动。如果只有点个灯的那点儿代码,那么可以用局域时钟。另外,现在 FPGA 的全局时钟 基本 16 个起,所以大多设计都可以直接用全局时钟进行驱动。

2、FPGA只要用到了PLL,一般出来就是全局时钟了。如果是直接外部时钟输入,经过一个全局BUF,你自己例化一个,就可以是全局时钟了。

3、顺便提一下,CMT即MMCM和PLL很重要,基本上咱们在使用FPGA时,外部输入时钟都需要先用CMT进行校正、去抖、分频等,其输出时钟才能被咱们使用。

4、FPGA的强大之处就是你可以把你的顶层模块中的信号任意指定于几乎是任意的管脚。当然时钟信号最好还是从专用的时钟管脚输入以保证最小的时延,也就是你所说的CLK0-CLK7。

5、没什么不妥当。用到几个就用几个就好了,不用的不用管。只要管脚分配和时钟约束做好就行。时钟约束最好约束成预期的110%,比如,你要跑50M,那你约束的时候就约束成55M,这是一般的经验。

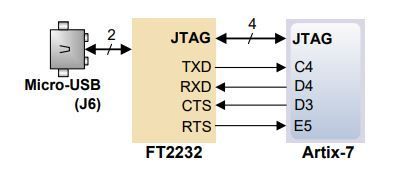

6、在用verilog语言设计好模块后,需要在软件中对输入和输出端绑定相应的引脚。不同的FPGA的系统时钟输入端的引脚是不同的,比如2C5Q208C8就是pin32(我记得),具体可以查阅相关芯片手册。

FPGA系统对系统时钟有何要求

,BUFG:其能被每个时钟区域内的SRCC、MRCC、CMT、GT、BUFR(不推荐)、其他BUFG;其可以驱动CMT、GT时钟、其他BUFG、FPGA内任何逻辑单元、BUFH。

是。对于7系列FPGA,需要对GT的这两个时钟手工约束;对于UltraScale FPGA,只需对GT的输入时钟约束即可,Vivado会自动对这两个时钟约束。用到几个就用几个就好了,不用的不用管,只要管脚分配和时钟约束做好就行。

不能自动确定的时候。XilinxFPGA常用时序约束详解中提到,工具并不能自动确定同步的时钟域之间的时钟时序关系,这个时候需要手动约束。FPGA即现场可编程门阵列,是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

FPGA设计中跨时钟域常见的问题(读书笔记)

从摘要中可以了解到这篇文章主要写了(1)亚稳态现象的出现(2)四种跨时钟域同步方案(3)评估分析(4)优化设计 可以理解为因为有跨时域的设计,在设计中容易出现亚稳态现象,所以要做好跨时钟域同步。

在同步设计中,最有效且目前应用最广泛的低功耗设计方法便是时钟控制——动态地禁止时钟在特定区域翻转。在FPGA中常用的实现方法包括使用触发器上的 时钟使能引脚 或者 全局时钟mux (BUFGMUX for Xilinx)。

亚稳态常见于异步电路。异步复位电路是常见例子,由于复位信号与时钟信号不同步,所以无法保证复位信号的移除时间和恢复时间满足要求,可能导致复位失败。跨时钟域数据传输时,由于两个时钟域信号变化不同步,也可能产生亚稳态。

在FPGA上实现时钟信号的多路同步输出该怎么做

将FPGA的时钟输出到其他电路板?是为了同步数据采集吗?一般不推荐将FPGA时钟引出的,买个时钟驱动芯片分路输出更好。

当想要将输入的脉冲信号FLAGIN_CLK同步成B时钟域的一个电平信号,只需要在脉冲同步电路后再加上一个信号延长电路, 意思就是当FLAGOUT_CLKB为高时,输出一个高电平并用计数器计数,计数器的计数值就是高电平的时间。

用时钟采样输入的数据,比较最后两次采样值,如果发生了变化,就产生一个开始发送的内部信号start_tx。然后用这个start_tx启动你的RS-232模块,把data_reg2分25个byte发送出去。

时钟偏移(Clock Skew):这是确保FPGA中不同模块能够同时接收时钟信号的过程。在高速系统中,时钟偏移是一个关键问题,因为它会影响系统的时序性能。

你的第一个程序,下面一个if并没有在敏感列表的clk下。

FPGA的时钟问题

FPGA不像单片机,可以有多个时钟。比如编程中always@(posedgeclk1)…always@(posedgeck2)…等等,实现不同部分不同频率处理。所以他没有所谓的默认时钟,每一个模块每一个同步处理代码都是需要自己制定用哪个时钟的。

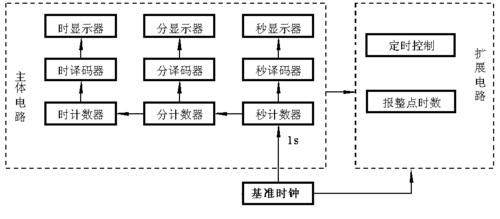

由于在FPGA设计中采用统一的系统时钟,也就是利用从全局时钟管脚输入的时钟。在一个FPGA设计中会用到多个时钟,每个时钟在FPGA内部形成一个时钟域。

理论上FPGA的任意一个管脚都可以作为时钟输入端口。

首先,是你对AD本身的概念没有理解清楚,AD都有时钟要求,不可能因为你的操作时钟的无限制增大而增大,这个一般取决于建立时间。另外,每个AD都有相应的转换时间。你的问题,可能是复位的问题。

有赋值符号 = 就可以了,这个符号是延迟一个时钟的。而 = 是不延迟的。

到此,以上就是小编对于fpga跨时钟的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏