本篇目录:

- 1、fpga读16位ddr3和32位ddr3

- 2、你的AD数据存在FPGA中去是这么实现的??

- 3、Win10创造者更新添新功能:未来将支持802.11ad标准

- 4、pcie时钟端接位置

- 5、FPGA如何实现高速AD采集

fpga读16位ddr3和32位ddr3

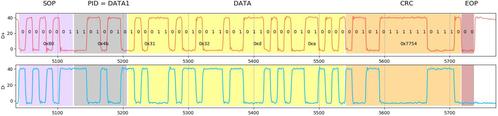

1、AXI4-Stream:用于高速数据流传输,非存储映射接口。AXI4 协议支持突发传输,主要用于处理器访问存储器等需要指定地址的高速数据传输场景。AXI-Lite 为外设提供单个数据传输,主要用于访问一些低速外设中的寄存器。

2、是一样的,一般用两片16位的DDR3构成32位存储器,这是两片DDR3的地址线和控制信号是共用的,但两片DDR3的数据线(DQ/DQS/DM)分别引到FPGA的不同的引脚。

3、DDR芯片安装不当。无法识别芯片类型或者驱动程序不正确等,还有可能是晶振安装错误或者与FPGA板不兼容等原因导致的。如果出现FPGA初始化DDR失败情况,建议通过检查DDR芯片、晶振等硬件设备以及驱动程序来解决问题。

4、DDR3是外部存储器,FPGA只是提供访问外部存储器的端口和控制器,一定是独立的。你说的读和写是不是对于一个外部DDR3存储器而言呢?对于同一个外部存储器,这当然不是问题,因为存储器肯定是要读和写的。

5、XILINX FPGA 中LUT 中移位寄存器的复用情况 一个LUT可以用于产生2个16bit移位寄存器,地址是复用的。

你的AD数据存在FPGA中去是这么实现的??

1、现在有一些FPGA内部已经集成了ADC模块,是能够实现ADC的功能的。如果是普通的纯逻辑阵列的FPGA芯片,一般都会外接ADC芯片来实现AD采样功能。

2、用verilog写AD和显示器的驱动,这种办法是最好的,因为FPGA的nios核不强大,用这种方法做出的示波器的频带能达到很宽。

3、我倒是有个建议,FIFO仍然按照同步进行设计,这样读写都是同样的速度,转到LCD这一端,将数据每隔固定点数进行摘取显示。

Win10创造者更新添新功能:未来将支持802.11ad标准

月1日消息微软今天为普通用户推送了Win10创造者更新预览版15046,与此同时微软还发布了Win10创造者更新15042预览版SDK下载和更新说明,主要包括Bug修复和API表面相关开发变化。

现在,微软终于向用户们推送了Windows10Mobile/PC创造者更新15014快速预览版。新版本沿袭了之前两次“海量”内容的做法,新增了不少新功能也修复了一些内容。本文首先介绍一下Win10Mobile/PC创造者更新15014的新增功能。

Win1时代更好,现在大致的分享页面UI早期成果也已经曝光如下。页面以小窗口形式,居于Win10系统桌面之上,应用采用网格状分布,分享方式更加简洁。Win10创造者更新将迎全新分享UI页面的资讯就为大家介绍到这里了。

除了以上新内容外,本次Xbox One版Win10创造者更新15026快速预览版还修复了上个版本的留存的一些Bug,但仍有大量已知问题存在。参加Xbox Insider的用户可以到设置系统主机信息更新中进行检查更新。

希望这些改进将使得用户更容易保持他们的机器安全。新的Windows Defender安全中心体验将面向每个人,从2017年的创造者更新版本开始。当然,在创造者更新中还有一大堆针对Windows 10用户的其他改进,目前正在通过Windows Insider测试。

我们相信,当硬件和软件完美配合时会产生特殊的化学反应,带来全新的深度体验,并开创一种全新的产品类别。今天,我们推出了另一种新的产品类别专门为创造者和专业人士所设计的全新Surface设备。

pcie时钟端接位置

pcie时钟门控设置?回答如下:时钟在连接网络下设置,需要设置pcle系统控制门控解决问题的计划清晰合理,问题的网友的认可度高。

主板没有pcie时钟电平解决办法:首先要先检查一下时钟芯片与其周边的电路是否有腐蚀或进入水现象。用万用电表的欧姆档去测量腐蚀位置。可以用其他接口配对,比如pci-e就可以转成pci,去网上商城搜pci-e转pci。

是可以接到0三使用的,但是会降速,目前根据你的主板看不太出来,标识可能会在后面,一般1位置是0,2位置是0,。你可以安装好后测一下速度,就可以分别出来了。

PCIeX1是PCIe接口中规格最小的一个,一般位置也距离CPU最远。常见需要使用到PCIeX1接口的硬件包括独立声卡、独立网卡,这些硬件一般都是因为主板的对应硬件性能无法满足用户需求而加装的,属于非必要升级硬件。

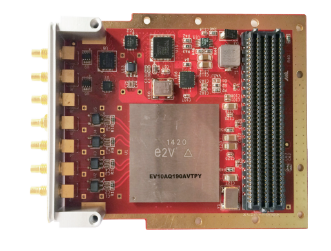

FPGA如何实现高速AD采集

如果是外挂AD芯片, 那么你需要查看ad芯片的DATAsheet,使用fpga设计响应的时序近而从AD获取转换后的数字值。

先例化一个sdram controller,再打个testbench,然后再build image,再上板测试。这可能是比较快的方式了。最好要对sdram的读写时序比较熟悉,然后例化的controller才能比较靠谱,如果能搞到sdram的bfm模型,那可能更好。

现在有一些FPGA内部已经集成了ADC模块,是能够实现ADC的功能的。如果是普通的纯逻辑阵列的FPGA芯片,一般都会外接ADC芯片来实现AD采样功能。

如果是调用IP core,到简单了,你在顶层文件里例化三个ipcore,然后用wire变量连接起来,就OK,按顺序连哦。。因为你没有说清楚DSP流程,我也不知道你要做哪些算法。。

FPGA:对ADC采样和存储器的控制。显示器和按键:主要做人机界面操作。)实际上显示和按键可以不加载FPGA上,也可以在你的电路系统中再加一块单片机,由那块单片机做人机交互,然后用指令的形式给FPGA发送各种命令。

fpga芯片能实现多路逻辑的并行输出,同时对一些频道的外部事件的响应可以快速响应。这些在单片机,dsp等处理器芯片上实现是比较困难的。处理器需要一条一条执行程序并给出逻辑输出电平,并发应差。

到此,以上就是小编对于高速数据传输接口的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏