本篇目录:

- 1、FPGA输出脉冲信号,经过2米长电缆宽度变宽是什么原因?

- 2、为什么要用fpga来实现千兆以太网传输速率

- 3、fpga线网型传输信号延时多大

- 4、怎样用低速FPGA芯片处理高速输入信号?谢谢!

- 5、画PCB时,FPGA芯片的最小间距是7mil,我连线的话地线,电源线,信号线只能...

- 6、请问下谁用FPGA做过irig-b对时啊,或者谁知道irig-b对时的原理啊,急求...

FPGA输出脉冲信号,经过2米长电缆宽度变宽是什么原因?

是因为这个信号的传输速率高,而且它的附带需要的信号速率也是非常大的。所以它的信号的线宽的两倍。

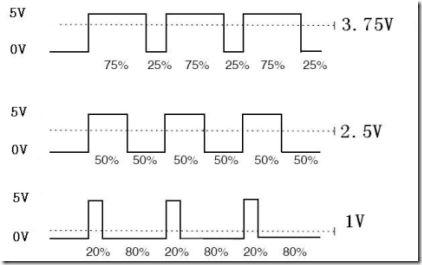

脉宽是10ns的话简单一点就用100MHz的时钟去计数。周期计数值设为1000000,脉宽计数值设为1就可以了。

与电平信号相比,脉冲信号在输入不变的情况下,仍然会发生周期性的变化,比如电平在高低之间不断反复,而且高电平和低电平维持的时间都相对固定。

(2) 用什么方法实现脉冲的产生。提供一个思路: 你可以设计2个RAM表(存数据),(可以用IP核)。

脉冲通常是指电子技术中经常运用的一种象脉搏似的短暂起伏的电冲击(电压或电流)。主要特性有波形、幅度、宽度和重复频率。脉冲是相对于连续信号在整个信号周期内短时间发生的信号,大部分信号周期内没有信号。

FPGA设计不是简单的芯片研究,主要是利用 FPGA 的模式进行其他行业产品的设计。 与 ASIC 不同,FPGA在通信行业的应用比较广泛。

为什么要用fpga来实现千兆以太网传输速率

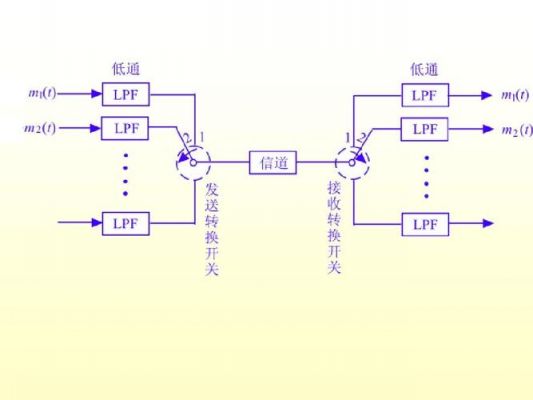

写了用以太网传输的优点,相对于串口的传输速度慢,并且不能远距离传输。PCIE不能远距离传输,选择以太网兼顾了传输速率和系统使用灵活的特点。

FPGA作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA设计不是简单的芯片研究,主要是利用 FPGA 的模式进行其他行业产品的设计。

以FPGA方式实现千兆以太网设计,有效提高了系统的可靠性和集成度,能够满足未来较长时间国内星载计算机系统在千兆以太网方面的实际应用需求。简介:88E1111是一款经典的三速以太网PHY芯片,可工作在10/100/1000Mbps下。

我对FPGA的了解还只是皮毛,以前也只做过FPGA+STM32以太网传输的项目,当时用FPGA只是因为它的速度快,其实这个和CPLD+单片机是相同的。你上面说了,它们三者单独都有这些能力,当然,这是在低速场合才成立。

问题三:千兆以太网和快速以太网的区别? 快速以太网(Fast Ethernet)也就是我们常说的百兆以太网,它在丹持帧格式、MAC(介质存取控制)机制和MTU(最大传送单元)质量的前提下,其速率比10Base-T的以太网增加了10倍。

千兆以太网是一种网络技术,它是以太网技术的一种演化。它使用了更高速的通信速度,可提供比传统以太网更快的数据传输速率。千兆以太网的速率可以达到1000Mbps,比传统以太网快10倍以上。

fpga线网型传输信号延时多大

1、普通FR4板材上传输时间约为每纳秒6英寸,根据你的走线长度即可计算出延时(注意:表层和里层走线稍微有点差别,表层速率大于里层)。

2、也就是你执行一次时延操作所用的时间即时延精度就是0.24us;如果是双周期指令就加倍。

3、fpga中异或门延时不得超过100ms。根据查询相关信息显示,fpga中异或门国家要求的延时时间不得超过100ms,就可以用FPGA去取代传统MCU去处理图像信息,来满足政府的延时要求。

怎样用低速FPGA芯片处理高速输入信号?谢谢!

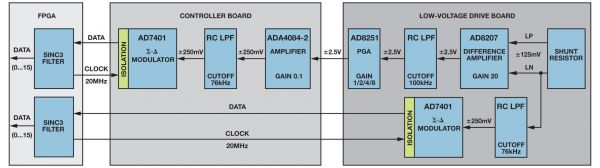

1、你需要处理1G的信号当然不是问题,主流的FPGA都支持高速串行接口,最高可以跑到25G。这么高速的信号进入FPGA会串并转换为几百兆的信号做处理,输出还可以再转为高速信号输出。

2、如果是外挂AD芯片, 那么你需要查看ad芯片的DATAsheet,使用fpga设计响应的时序近而从AD获取转换后的数字值。

3、Quartus 0是支持CycloneIII的器件的,需要你在器件列表里选好型号,同时如果从一个芯片移植到另一个芯片,建议一个模块一个模块移植,而不是直接更改芯片信号,容易出错。边移植边编译,根据编译警告来解决问题。

4、这一点很容易想,对厂家来讲不会做这种给竞争者提供服务事情的。IP厂商一般会高价的提供未加密的RTL级源码,有时FPGA厂商为了扩大芯片市场占有率,会购买第三方的IP做进一步的处理后免费提给该FPGA芯片使用者的。

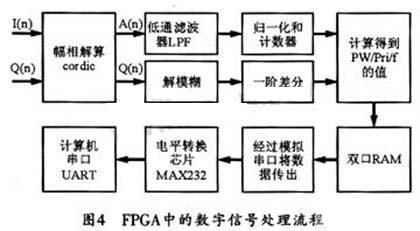

5、一般信号处理系统是前面一个高速的AD,然后把数据送给FPGA(直接送给CPU的话,CPU速度跟不上),FPGA后接缓存,然后把数据送给CPU处理。

6、在处理视频信号时,FPGA芯片可以充分利用自身的速度和结构优势,实现乒乓技术和流水线技术。在对外连接的过程中,芯片采用数据并行连接的方式,使图像信息的位宽拓宽,利用内部的逻辑功能提高图像处理的速度。

画PCB时,FPGA芯片的最小间距是7mil,我连线的话地线,电源线,信号线只能...

1、你说的完全没错,在FPGA芯片周边的布线宽度只能根据FPGA芯片的间距来设定规则,并需要按照此原则布线。在其它地方可以加宽、加大尺寸,目前的PCB制作技术水平完全没有问题,0.1mm的线宽可以满足使用。过宽,布通率会受到影响。

2、BGA封装的话电源和地都是一般就近在四周焊盘中间空余位置打过孔(连接到电源层或地层),线长6mil就可以,过孔是外28,内12的。电源附近有位置的话放去耦电容。一般的表贴的话就要看引脚的宽度了。

3、一般正常情况下线宽线距控制到6/6mil,过孔选择12mil(0.3mm),基本80%以上PCB生产厂商都能生产,生产的成本最低。

4、尽量加宽电源线、地线宽度,最好是地线比电源线宽。它们的关系是:地线>电源线>信号线,通常信号线宽为:0.2~0.3mm,最经细宽度可达0.05~0.07mm,电源线为2~5 mm。

5、一般线宽线距控制到 6/6mil ,过孔选择 12mil(0.3mm),大部分的PCB生产厂商都能生产,并且生产的成本低。

请问下谁用FPGA做过irig-b对时啊,或者谁知道irig-b对时的原理啊,急求...

IRIG是美国靶场仪器组的简称。IRIG时间标准有两大类:一类是并行时间码格式,这类码由于是并行格式,传输距离较近,且是二进制,因此远不如串行格式广泛;另一类是串行时间码,共有六种格式,即A、B、D、E、G、H。

时钟振荡器随时间产生漂移,需要标准授时系统作校准,校准过程要缩短和安全可靠。

编码对时目前常用的是IRIG-B对时,分调制和非调制两种。

IRIG-B(DC)直流偏置信号接口 每秒1帧,包含100个码元,每个码元10mS。脉冲宽度编码,2mS宽度表示二进制0、分隔标志或未编码位,5mS宽度表示二进制1,8mS宽度表示整100mS基准标志。

IRIG-B(简称B码)是专为时钟串行传输同步而制定的国际标准,采用脉宽编码调制。同步时钟源每秒发出一帧含有秒、分、时、当前日期及年份的时钟信息。

到此,以上就是小编对于fpga参数传递的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏