本篇目录:

iic的数据传输

1、IIC(Inter-Integrated Circuit) ,简单说就是IC(芯片)之间通信的总线。总线的意思就是,各个器件都并联接到一组公共的线路上,然后共用这条线路来传输数据信息。

2、在IIC中,多个芯片可以连接到同一总线结构下,同时每个芯片都可以作为实施数据传输的控制源,这种方式简化了信号传输总线。谢谢。

3、在I2C总线传输过程中,将两种特定的情况定义为开始和停止条件(见图3):当SCL保持“高”时,SDA由“高”变为“低”为开始条件;当SCL保持“高”且SDA由“低”变为“高”时为停止条件。开始和停止条件均由主控制器产生。

4、连接到相同总线上的IC数量只受总线最大电容的限制,串行的8位双向数据传输位速率在标准模式下可达100Kbit/s,快速模式下可达400Kbit/s,高速模式下可达3.4Mbit/s。

请问模拟的iic时序读取数据的时候错误,有什么办法防止!谢谢了,大神...

1、读数据,首先为起始信号-》从地址(最后一位为W写)-》重复起始信号 -》从地址(最后一位为R读)-》存放的寄存器地址或读的数据地址- 读到的数据。这么个过程。不懂的可以接着问。

2、io口加上上拉电阻或者降低传输速度就能彻底的解决你的问题。

3、数据重新发送,以覆盖原来的错误 设置合理的超时时间,以在超时后允许系统重发。对于重要数据,比如需要保存的系统参数,在无应答信号时,需要将数据读回进行校验,防止出现写错误。

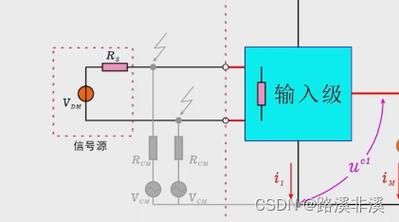

4、简单说一下吧,就是SDA控制权在切换过程时需要一点时间,不是无缝衔接。切换间隔时间内,SDA被外部上拉拉高电平导致的。这个不影响通信,就是波形不完美。如果MCU时用IO模拟IIC通信协议的话,这个问题可以轻松解决。

IIC通信的时序图问题

摘要:介绍模拟I2C总线的多主节点通信原理,并提出一种新的实现方法。这种采用延时接收比较来实现仲裁的方法,可使不具有I2C接口的普通微控制器(MCU)能够实现模拟I2C总线的多主通信,同时对I2C总线的推广起到了积极作用。

IIC 接口 只有两个通信线SCL和SDA,SCL是时钟信号,SDA是数据线。

IIC总线的时序,好像是:最高频率在400KHz。单片机指令的执行时间,速度快,所以要加延时。停止函数,是在SCL=1期间,SDA出现上升,那么SDA先要为0,这个0,要在SCL=0实现。

读数据,首先为起始信号-》从地址(最后一位为W写)-》重复起始信号 -》从地址(最后一位为R读)-》存放的寄存器地址或读的数据地址- 读到的数据。这么个过程。不懂的可以接着问。

I2C总线的小问题,求大神!在线等

像你说的,直接产生SCL方波,然后从start时序开始你要从头到尾严格通过定时器延时来控制整个传输过程SDA线的变化,类似面向过程来编程。

首先确认你的I2C的速率,软件模拟的话就与MCLK直接相关了,自然单片机的速率下降就会正常;如果是硬件I2C的话需要看时钟来源是不是MCLK并作修改。看你的电路并没有进行上拉也就是SDA和SCL需要接7K或者10K的电阻至VCC即可。

I2C总线理解上的难点就是在于 ACK和NACK的使用上,估计你就没看明白I2C协议。

因为I2C总线规范就是这样定义的。如果不符合这样的要求,I2C总线就定义为起始位或者停止位。起始位的定义:时钟为高电平时,SDA 线上的电平由高变为低;停止位的定义:时钟为高电平时,SDA 线上的电平由低变为高。

到此,以上就是小编对于iic接口时序的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏