本篇目录:

DSP是否支持LVDS接口?

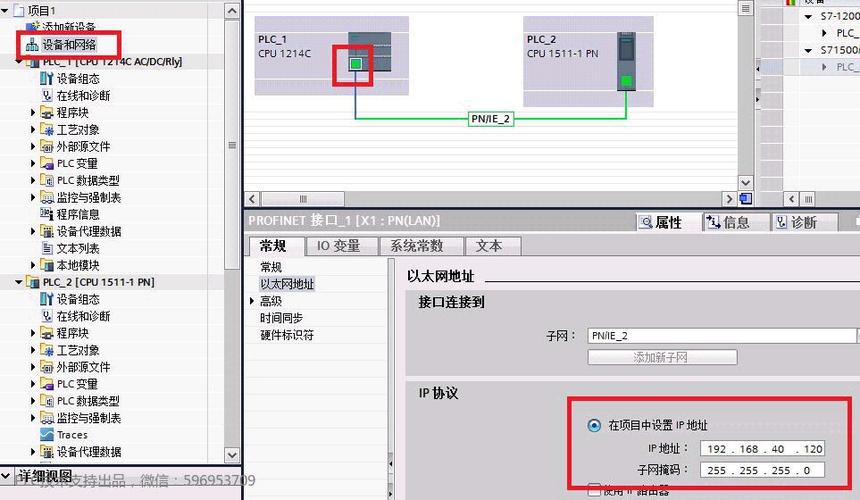

1、LVDS是一种低压差分电平,通常FPGA和MAX V 系列的CPLD会带有这种接口,2812是没有这种接口的,你可以换成用并行异步总线的AD。

2、那要看DSP有什么接口。目前似乎还没看到有DSP带高速串行接口的,用的更多的是并行的LVDS接口,数据带宽也够宽了。

3、如果不在一块板子上,速度慢可以RS485,速度快得可以使用LVDS传输。

4、数字显示接口:LVDS线可以将计算机中的数字信号转换为适用于数字显示器的信号,用于数字电视机、电子看板、广告机和监视器等的信号传输。嵌入式系统:LVDS线在嵌入式系统中的应用较为广泛,如DSP芯片、FPGA、LPDDR等。

5、软件层面的不同。在软件层面上,给DSP写程序和给多核CPU写程序,给GPU写程序,没有太大区别,DSP有完善的C语言编译器。目前高端的FPGA中都集成了硬核DSP。编程语言不同。

6、FPGA可以完成电平转换、串并转换、一些DPS运算等处理。简单的说,如果AD处理是高速串行接口,就不能直接进DSP,需要先进FPGA转成DSP可以接受的LVDS信号。

基于CPLD多串口通信

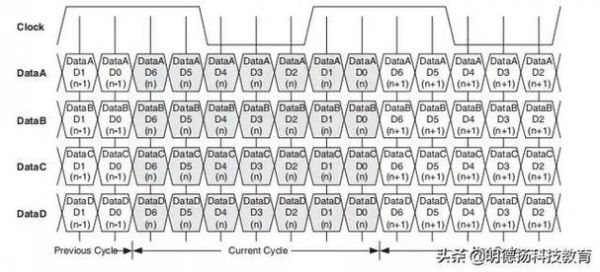

1、接收一个端口,发送一个端口,时钟信号一个端口,寄存器,串并转换,计时器,分频器(一般分为9600BAND),串行发送,接收。

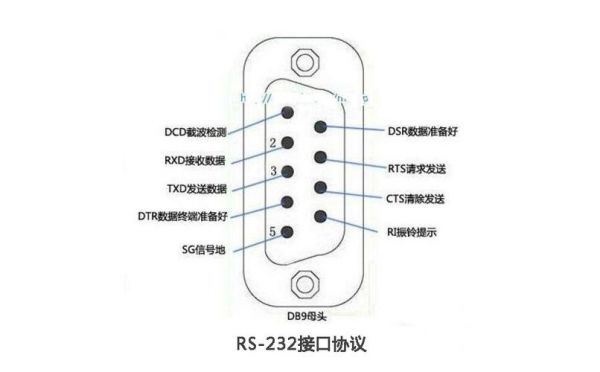

2、你这个情况十之八九是线用错了,串口线有交叉的,有直联的,2和3脚两要线交换一下试试。你用万表量一下PC出来的2和3,-10V就是PC机的发,另一个就是PC的收。把收和发理清楚就OK了。

3、通信方式有两种:串行通信方式和并行通信方式。并行通信方式如:PLC模块的背板总线、工控机的运行狗。RS232和RS485都是基于串口通信的方式。工业控制的RS-232口一般只使用RXD、TXD、GND三条线。

4、BEGIN bidir = from_core WHEN oe=‘1’ ELSE “ZZZZ”;to_core = bidir;END behavior;你要3选1,但是双向口描述的时候建议在参考上面结构的同时,把选择信号KE嵌套到if里去&一下,不要用case语句。

5、cpld是可编程器件,通信方式可以自己设定。

6、见你写了这么多,看了不回答都不好意思了。这种干扰是一方面来自于你的外部5V电源地干扰,很多5V电源质量很差的。

简述基于eda软件的fpga/cpld设计流程主要包括哪几个步骤

1、EDA技术的设计流程:设计输入用一定的逻辑表达手段表达出来。逻辑综合将用一定的逻辑表达手段表达出来的设计经过一系列的操作,分解成一系列的逻辑电路及对应关系(电路分解)。

2、通常可将FPGA/CPLD设计流程归纳为以下7个步骤,这与ASIC设计有相似之处。设计输入。Verilog或VHDL编写代码。前仿真(功能仿真)。设计的电路必须在布局布线前验证电路功能是否有效。

3、FPGA 的设计开发流程主要包括四个步骤:设计输入(Design Entry)、仿真(Simulation)、综合(Synthesis)及布局布线(Place & Route)。

4、现代数字系统的设计流程是指利用EDA开发软件和编程工具对可编程逻辑器件进行开发的过程。在EDA软件平台上,利用硬件描述语言HDL等逻辑描述手段完成设计。

到此,以上就是小编对于lvds数据传输的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏