本篇目录:

- 1、请问FPGA与DSP之间怎么进行数据传输,能细致的叙述下吗

- 2、fpga与电脑通信,应该考虑哪些问题,同时fpga上没有了usb、spi接口了,要...

- 3、关于FPGA通过以太网向上位机发送数据包的问题

- 4、两块fpga光纤不通

- 5、开发环境与FPGA原理介绍?

- 6、fpga差分信号输出可以同时接两个输入么

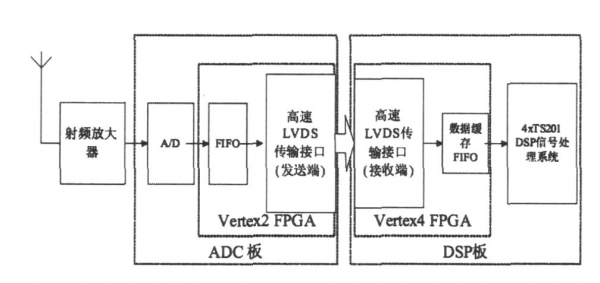

请问FPGA与DSP之间怎么进行数据传输,能细致的叙述下吗

找一款简单的dsp芯片,比如ti的54系列,看看emif接口,fpga可以跟emif挂接,然后用emif的读写来操作fpga内部逻辑。不过,fpga的逻辑时序要符合dsp的emif接口时序。先把dsp看好。

如果你的引脚资源足够,当然完全可以直接用并行传输的方式,速度超级快,又没有复杂的协议。

方法多了,挂总线式的话,你设计就要将DSP的几根地址线接到FPGA上。然后直接像操作外部寄存器一样就ok了。如果是基本的IO连接到FPGA上,那你就自己在FPGA里面写个接口程序。

fpga与电脑通信,应该考虑哪些问题,同时fpga上没有了usb、spi接口了,要...

这其中,以太网端口速度比较快,带宽比较宽。你只要在DE2上开发好板上以太网的驱动就可以与PC机通过网线(交叉线)或者交换机(平行线)来实现数据传递了。

fpga连接电脑网口没反应原因如下:fpga连接口使用时间长,造成了fpga连接口的损坏。fpga连接线长时间使用断裂,电路不同,电脑没有反应。

比如简单的并行通信,就是一对一的IO口,这种都不需要什么通信协议。还有就是确定一种通信协议,如I2C,SPI,PCI等等,确定了通信协议,FPGA几乎都能实现。

FPGA不同于ARM和单片机。FPGA里面没有指令,没有定时器,甚至可能连个基本的乘法器都不能直接使用。而要使用FPGA,你要考虑的不是软件的流程,而是硬件的组合。FPGA的经典结构是:触发器+查找表。触发器做时序逻辑电路。

FPGA学习重点 看代码,建模型只有在脑海中建立了一个个逻辑模型,理解FPGA内部逻辑结构实现的基础,才能明白为什么写Verilog和写C整体思路是不一样的,才能理解顺序执行语言和并行执行语言的设计方法上的差异。

关于FPGA通过以太网向上位机发送数据包的问题

1、这其中,以太网端口速度比较快,带宽比较宽。你只要在DE2上开发好板上以太网的驱动就可以与PC机通过网线(交叉线)或者交换机(平行线)来实现数据传递了。

2、接受上机位的ARP请求,提取上位机的MAC地址和IP地址,以及接收上位机的UDP数据包,并提取报文。发送模块 发送ARP应答给上位机,封装要发送的数据,加上UDP首部,IP首部以及以太网帧首部,并发送给MAC层的ip核。

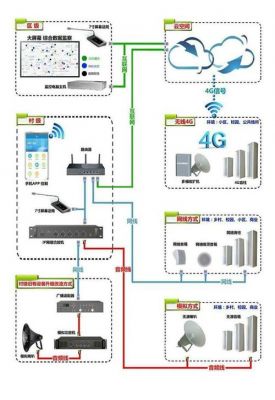

3、综合考虑到测试系统实时性和可靠性的要求,选择以太网口作为数据传送总线变换器与上位机的数据转发接口,以高速串口作为控制口,采用FPGA+DSP+ARM的架构作为实时信息处理平台。数据传送总线变换器的系统框图如图1所示。

4、通过USB传输给上位机。FPGA打包在某红外图像采集系统中,对采集到的图像数据处理后打包通过USB传输给上位机。

5、看有没有问题。如果上位机不能自发自收,那就是串口线损坏或上位机使用的串口工具的问题了。如果上位机能自发自收,示波器又能正确接收FPGA发送的数据,那只能是串口工具的设置不当了。

6、不是已经说了嘛,使用串口进行数据传输,不过由于是多组FPGA,如果需要将数据传输到指定的FPGA上的某个寄存器需要对串口的数据格式进行定义,也就是说需要自己制定一个简单的协议。

两块fpga光纤不通

fpga在线烧录网络正常,固化进去,网络不通解决方法如此。把USB线插到主机箱背后。右键点击电脑,管理。设备管理器,光驱禁用。外置刻录光驱USB,重新换一个盒子。

两块FPGA之间通信有很多种方法,具体看你的需求了。比如简单的并行通信,就是一对一的IO口,这种都不需要什么通信协议。还有就是确定一种通信协议,如I2C,SPI,PCI等等,确定了通信协议,FPGA几乎都能实现。

数据位宽和读写使能等,配置好以后,利用FPGA将双口RAM核调用就可以实现FPGA与双口RAM之间的通信了。那么两块FPGA与双口RAM的通信之间的通信也就是双口的读写过程。不过不知道你为什么要用两块FPGA来与双口RAM之间通信。

fpga随着计算机性能的不断提高,gtxbank的时钟频率以及计算机外围接口的带宽成指数地增长,这导致处理器的数据吞吐量也相应的增加。

需要有PC端的通讯卡。然后对接就可以进行通讯了。

这么简单还用问?不同always块不能对相同寄存器进行赋值。这样会照成多驱动。

开发环境与FPGA原理介绍?

1、\x0d\x0a\x0d\x0a4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。 \x0d\x0a\x0d\x0a5) FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

2、需求分析和规划 在开始FPGA开发之前,首先需要明确应用场景和需求,例如数据加速、信号处理、图像处理等。根据需求,进行系统架构规划和算法设计。

3、FPGA作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA设计不是简单的芯片研究,主要是利用 FPGA 的模式进行其他行业产品的设计。

fpga差分信号输出可以同时接两个输入么

第一种方式是先使用IBUFGDS将差分时钟转换成单端时钟,然后送入PLL进行分频。此时PLL的输入时钟的source选择单端时钟即可。第二种方式是直接使用PLL同时完成差分信号到单端时钟的转换和分频。

不同。差分放大电路的输出值和是单端输入还是双端输入没有关系,只和输出有关。如果是双端输出的那么差模增益等于对应组态的单管放大电路的电压增益值;如果是单端输出的,那么差模增益等于双端输出差模增益的一半。

将两路输入信号转换为一路信号并输出两路信号可以通过混音器来实现。混音器是一种音频设备,可以将多个音频信号混合在一起,并输出为一路信号。

Xilinx:需要在程序中显性的表示出有2个时钟输入端,在程序内部将这两个差分成对的时钟送入一个IBUFGDS(在ISE 的language assistant中有模板)。

而正端输入则包含了干扰信号信号,差分输入就包含干扰信号。而双端输入情况下,共模干扰并不影响两个输入端之差值,相当于抑制了共模干扰。接法是这样,但放大对象不一样。双端输入,放大的是两个输入端之间的差值。

要用差分布线一定是信号源和接收端也都是差分信号才有意义。所以对只有一个输出端的时钟信号是无法使用差分布线的。

到此,以上就是小编对于fpga 差分转单端的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏