本篇目录:

- 1、基于CPCI系统的高速数字通信接口电路设计与应用

- 2、两次udp发送时间间隔

- 3、基于FPGA的千兆以太网数传系统设计

- 4、fpga接收udp数据丢帧

- 5、可靠UDP协议栈的FPGA实现

- 6、FPGA和PC端MFC程序进行UDP通讯

基于CPCI系统的高速数字通信接口电路设计与应用

在CPCI系统环境下高速数字通信AFDX协议端系统接口的电路设计与功能实现。采用Verilog编程实现基于FPGA的硬件设计部分,采用C编程实现基于MicroBlaze的嵌入式软件设计。 0 引言 随着通信技术的高速发展,嵌入式系统对数据传输速率的要求更高。

BWDSP100处理器具有丰富的接口资源,在应用系统开发时,可以将多片DSP处理器组合,形成功能更加强大的板级应用系统。

数据采集的概念,是指从传感器和其它待测设备等模拟和数字被测单元中自动采集信息的过程。数据采集系统是数据采集结合基于计算机的测量软硬件产品来实现灵活的、用户自定义的测量系统。

U就是高度,有些欧洲厂家也把它叫做HE。具体说来,就是CPCI电源立起来的尺寸。1U=75英寸=445毫米。

CPCI是基于PCI电气规范开发的高性能工业总线,适用于3U和6U高度的电路插板设计。CPCI电路插板从前方插入机柜,I/O数据的出口可以是前面板上的接口或者机柜的背板。

与此同时,CompactPCI/PXI技术也逐渐被国内市场接纳和认同,应用气氛十分活跃。 CompactPCI简称cPCI,中文又称紧凑型PCI,是国际PICMG协会于1994提出来的一种总线接口标准。

两次udp发送时间间隔

某一IP连续多次连接本机的NetBios-SSN[139]端口,表现为时间间隔短,连接频繁。此时日志中所列计算机感染了“尼姆达病毒”。

心跳包是用来维护TCP/IP链路的畅通,防止自动掉线。

UDP可以使用于实时聊天,对数据准确性和丢包要求比较低,但速度必须快,还有视频直播,只需要保证视频连续就行,偶尔网络问题丢包不影响观看;TCP的话就很多了。

-i seconds 在两次数据包发送之间间隔一定的秒数。不能同-f一起使用。 -n 只使用数字方式。在一般情况下ping会试图把IP地址转换成主机名。这个选项要求ping打印IP地址而不去查找用符号表示的名字。

设置间隔小就好了,根据网络资料查询显示增加系统发送或接收缓冲区大小intnBuf=32*1024。//设置为32K即可。

基于FPGA的千兆以太网数传系统设计

写了用以太网传输的优点,相对于串口的传输速度慢,并且不能远距离传输。PCIE不能远距离传输,选择以太网兼顾了传输速率和系统使用灵活的特点。

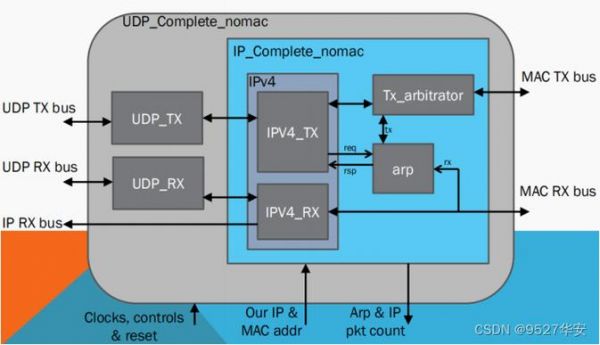

以FPGA方式实现千兆以太网设计,有效提高了系统的可靠性和集成度,能够满足未来较长时间国内星载计算机系统在千兆以太网方面的实际应用需求。简介:88E1111是一款经典的三速以太网PHY芯片,可工作在10/100/1000Mbps下。

百兆以太网应用场景广,适用于突发通信和继续传送大型数据文件,互换操作性好,具有广泛的软硬件支持。

一般的ip核都有自动生成工具,比如Altera有megacore wizard,按照你需要的功能enable或者disable选项就可以了。具体步骤可以上Altera或者Xilinx的网站,搜索你需要的以太网ip核关键字,比如GE或者FE,以及是否需要MAC,PCS功能等。

您甚至可能希望随时重新配置FPGA,改变外设。 开发基于FPGA的外设系统相对简单,FPGA供应商提供IP库以及基于GUI的设计工具,使您很容易连接外设IP和硬核处理器。对此,设计流程与使用Nios II处理器等软核CPU的流程完全相同。

fpga接收udp数据丢帧

异步传输在传输打速率信号时是会出现帧失步的,建议你换种传输方式吧。用SDH(同步数字光传输)这样会好很多。

信号连接错误,时序约束问题。信号连接错误:在例化时,需要正确连接输入和输出信号,如果信号连接错误,会导致数据无法传递,检查信号连接是否正确,特别是时钟信号和复位信号。

fpga一根输入线让它数据稳定下来的办法,FPGA的程序最终是要固化到硬件上,设计FPGA程序等同于设计一个PCB,或者设计一个芯片,该芯片的一切功能都是由你来控制的。

FPGA的输出方向,输出延时output delay在有无signal tap ii时发生变化,造成MII时钟和数据的相位关系改变,或者说开始对方芯片时钟可以采到正确的数据,但output delay变化后时钟采不到正确的数据。时钟频率约束。

可靠UDP协议栈的FPGA实现

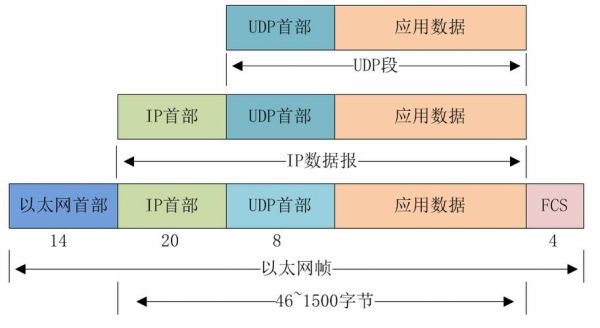

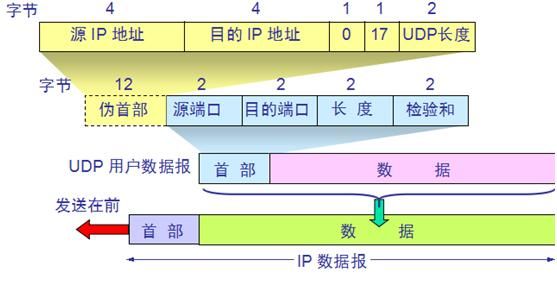

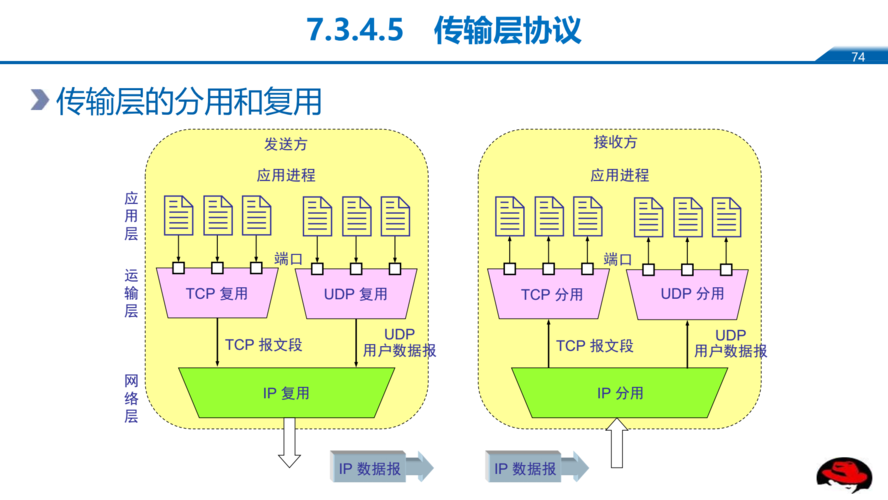

1、IP数据报首部协议字段是否为0x11 ip报部分的目的IP地址是否和本地地址一样 udp首部的目的端口号是否和本地的端口号一样 若判断通过,就将UDP数据存入接收FIFO中,同时记录数据长度为frame_cnt。

2、并实现了使用FM无线传输音频信号,以及使用ASK无线传输文本与图片。最后对FM及ASK实现的性能进行了分析,提出了部分适用场景。

3、分包与重组的过程是肯定要有的,但问题是 UDP 的传输方式不保证可靠性,但是文件传输必须要可靠,这一点你想怎么解决,我的看法是你需要在你的协议中解决这个问题,为了增强可靠性就需要在你的程序中实现接让收方发送回执。

FPGA和PC端MFC程序进行UDP通讯

1、分包与重组的过程是肯定要有的,但问题是 UDP 的传输方式不保证可靠性,但是文件传输必须要可靠,这一点你想怎么解决,我的看法是你需要在你的协议中解决这个问题,为了增强可靠性就需要在你的程序中实现接让收方发送回执。

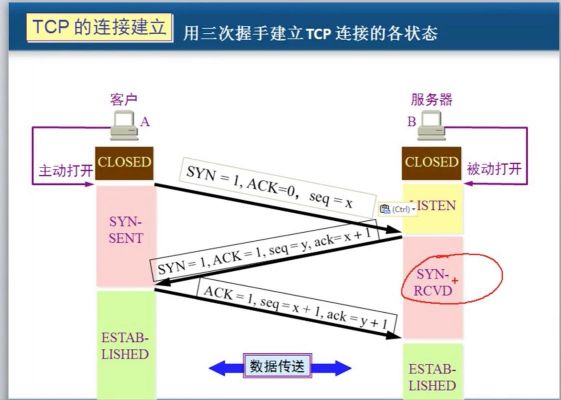

2、采用VHDL硬件描述语言,并运用模块化的设计理念,参考TCP_IP协议栈的工作机制,设计并实现了一个具有接收确认及漏发重发功能的可靠的UDP_IP网络通信协议栈。

3、UDP发送数据时,用SendTo函数试试。

4、将固定带宽分配给每个VL,等价于把接收端与发送端之间的数据传输限制在一个BAG内,即在一个BAG内只有一次数据传输,如果数据包过大,将其分为多个帧进行发送,也将会在各自的BAG内进行发送。

5、UDP是一个无连接协议,传输数据之前源端和终端不建立连接,当它想传送时就简单地去抓取来自应用程序的数据,并尽可能快地把它扔到网络上。

6、FPGA的输出方向,输出延时output delay在有无signal tap ii时发生变化,造成MII时钟和数据的相位关系改变,或者说开始对方芯片时钟可以采到正确的数据,但output delay变化后时钟采不到正确的数据。时钟频率约束。

到此,以上就是小编对于fpga udp的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏