本篇目录:

- 1、电路求电流问题?

- 2、CPU电路图怎么设计出来的?

- 3、迟滞比较器运放怎么选择

- 4、电荷泵锁相环电路的优点

- 5、集成电路设计需要哪些软件

电路求电流问题?

1、原理式:电流=单位时间通过的电量=Q/t。

2、电流的计算需要具体问题具体分析,不同情况下计算方式也不同 一般情况下计算电流用欧姆dao定律,欧姆定律定义式:电流=电压÷电阻。原理式:电流=单位时间通过的电量=Q/t。

3、电流的计算需要具体问题具体分析,不同情况下计算方式也不同:一般情况下计算电流用欧姆定律,欧姆定律定义式:电流=电压÷电阻。原理式:电流=单位时间通过的电量=Q/t。

4、串联电路电流求解方法如下:若已知某一处的电流,则整个电路电流为这一处的电流,原因是串联电路中电流处处相等。根据欧姆定律电流等于电压除以电阻,电阻为串联电路的总电阻,电压为串联电路的总电压。

5、串联电路:总电压等于各部分电路两端电压之和。并联电路:各支路两端电压相等,且等于电源电压。以上是电路的电压和电流的基本计算方法,需要注意的是,在交流电路中,电流的计算稍微复杂一些,需要考虑交流电压随时间变化的情况。

6、解:I=5/(2+3)=1(A)。所以:VB=2×I=2×1=2(V)。节点B、C间的电阻无电流流过,所以VC=VB=2V。UAC=1×4=4(V)。所以:VA=UAC+VC=4+2=6(V)。

CPU电路图怎么设计出来的?

用Protel DXP 2004之类的软件画出来的。调用元件库中的元件,就可以画出。如下图就是Protel DXP 2004中Z80CPU的元件。

在经过热处理得到的硅氧化物层上面涂敷一种光阻(Photoresist)物质,紫外线通过印制着CPU复杂电路结构图样的模板照射硅基片,被紫外线照射的地方光阻物质溶解。

掩模上印着预先设计好的电路图案,紫外线透过它照在光刻胶层上,就会形成微处理器的每一层电路图案。一般来说,在晶圆上得到的电路图案是掩模上图案的四分之一。光刻:由此进入50-200纳米尺寸的晶体管级别。

迟滞比较器运放怎么选择

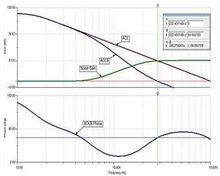

低频时可以考虑的方式有低通、带通或全通,同时还可选择一阶或多阶。在考虑此设计后,一阶滤波器在此设计中是较好的,且低通 滤波器是相对比较简单的,所以设计选择低通滤波器。简单低通滤波器通常可由电容与电阻组成。

分析计算过程,回差的要求和供电Vcc是已知条件,那么选定一个Uref,通过计算可以得到R1,R2,R3,R4的值,选择合理的R5即可以得到需要的上限和下限电压。下限电压=上限电压-ΔU。

同相滞回比较器:当输入的比较电压相对于参考点电压的大小,如果大于参考点,则输出高电平,反之则输出低电平。反相滞回比较器:电路接法是参考点位来自本比较器的输出端,并接在同相端,输入信号接在反相端。

引入正反馈,系统可能震荡,适当加入,可以产生迟滞(回差)。放大器一般引入负反馈,可得到固定的放大倍数。环的概念:信号-检测-和标准比较-再控制输入信号的某个参数,使其达到标准。

一般运放的差模开环直流电压增益在 80~120dB之间。实际运放的差模开环电压增益是频率的函数,为了便于比较,一般采用差模开环直流电压增益。(7)共模抑制比:共模抑制比定义为当运放工作于线性区时,运放差模增益与共模增益的比值。

供参考:当输出为高电平(稳压管钳位在4V)时,运放同相端为2V。

电荷泵锁相环电路的优点

1、电荷泵锁相环(charge pump phase-locked loop,CPPLL)因其自身所具有的开环增益大、捕获范围宽、捕获速度快、稳定度高和相位误差小等优势,现已广泛应用在无线通信领域中。在整个电荷泵锁相环系统中,电荷泵电路起着非常关键的作用。

2、它通过生成和注入电荷来调整相位,并通过锁相环控制器来维护相位。CPPLL的优点在于简单、低成本和低功耗,适用于高速数字电路中。

3、电荷泵锁相环有两个突出的优点:(1)捕获范围仅仅由压控振荡器的输出频率决定;(2)如果忽略失配与偏差,静态相位误差为零。

集成电路设计需要哪些软件

Altium Designer:功能较为全面,支持高阶绘图、PCB 菜单设计等,广泛用于商业电路板设计和生产领域。OrCAD:集成套件,市场占有率较高。拥有友好易用的界面,多种绘制选项,涵盖从较简单的电路至复杂的设计图形。

我也是微电子的,我们现在的毕业设计都是用maxplus或者quartus做。其他学习的软件还有cadence,画版图的tanner啊等等。做数字集成电路verilog是肯定要学的,还有vhdl啊等等。

快速设计电路图的软件有Eplan电气绘图软件、Elecworks电器绘图软件、Protel电路绘图软件等等,设计电路图的软件种类其实也很繁多,每种设计软件都有它自身侧重的特点,使用什么样的绘制电路图软件还需要结合自己的实际需求。

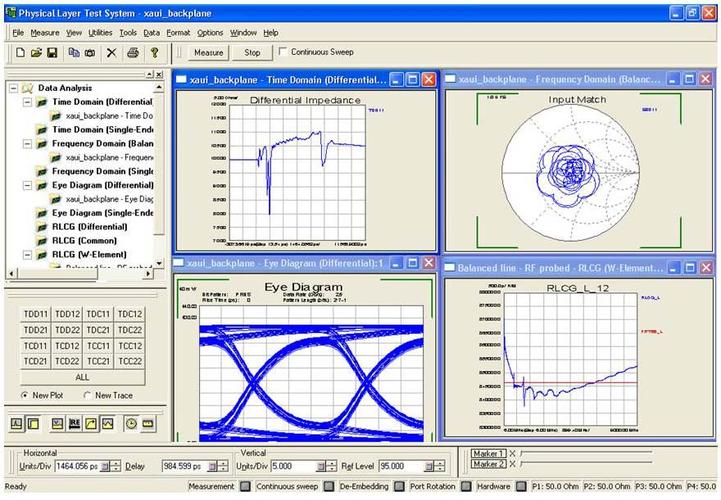

Cadence Allegro Cadence Allegro系统互连平台能够跨集成电路、封装和PCB协同设计高性能互连。应用平台的协同设计方法,工程师可以迅速优化I/O缓冲器之间和跨集成电路、封装和PCB的系统互联。

PADSLayout(PowerPCB)提供了与其他PCB设计软件、CAM加工软件、机械设计软件的接口(),方便了不同设计环境下的数据转换和传递工作。Cadence CadenceAllegro系统互连平台能够跨集成电路、封装和PCB协同设计高性能互连。

到此,以上就是小编对于传输线是啥的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏