本篇目录:

什么是SDH(数字电路)??

数字电路是用数字信号完成对数字量进行算术运算和逻辑运算的电路。由于它具有逻辑运算和逻辑处理功能,所以又称数字逻辑电路。现代的数字电路由半导体工艺制成的若干数字集成器件构造而成。逻辑门是数字逻辑电路的基本单元。

SDH数字电路(Synchronous Digital Hierarchy)业务是指为用户提供传输速率为048Mbits/s的数字传输电路。 2M是数字通信的一个基本速率(一个E1即为一个2M)。

数字电路/用户基础数字电路是指基于电信的SDH网络,实现客户内部网点的线路连接,完成数据、话音、图像等数据的传输。

数字专线(SDH):英文名为SDH(Synchronous Digital Hierarchy,即同步数字体系)专线,中文名为数字专线。是利用光纤、数字微波、卫星等数字电路开放的数据传输业务。

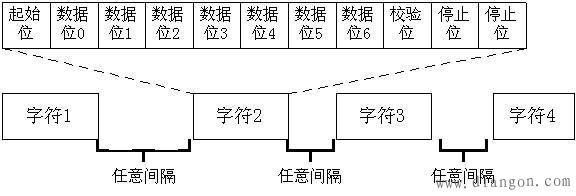

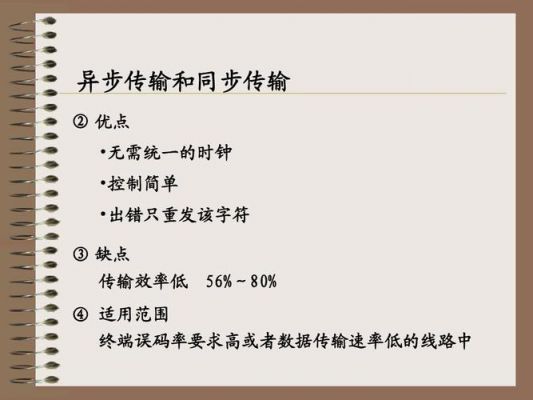

同步时序电路比异步时序电路工作慢

异步的就是各个集成块的CP脉冲不是同一个,一般可能是后级往前级送。由于信号的传递需要时间,异步时序电路的速度会比较慢。

原理不同 同步电路利用时钟脉冲使其子系统同步运作,而异步电路不使用时钟脉冲做同步,其子系统是使用特殊的“开始”和“完成”信号使之同步。

异步电路非常容易产生毛刺,且易受环境的影响,不利于器件的移植。

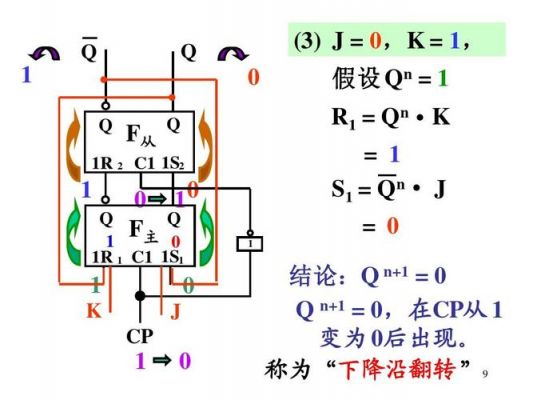

同步时序电路和异步时序电路比较,其差异在于后者()。

在同步时序电路中全部触发器均用同一个外部时钟脉冲cp触发。而在异步时序电路中各触发器则可以采用不同的时钟信号触发。

在同步时序电路中全部触发器均用同一个外部时钟脉冲CP触发。而在异步时序电路中各触发器则可以采用不同的时钟信号触发。

时钟电路原理及原理图

1、结构图如下:电子钟是一个将“ 时”,“分”,“秒”显示于人的视觉器官的计时装置。它的计时周期为24小时,显示满刻度为23时59分59秒,具有校时功能和报时功能。

2、利用预置数反向LD端实现异步置数。当Rd=0,且反向LD=0时,不管CPu和CPd时钟输入端的状态如何,将使计数器的输出等于并行输人数据,即Q3Q2Q1Q0=D3D2D1D0。

3、主要用于提供时钟信号以控制数据的输入与输出;I/O为输入输出设备,用作三线接口时的双向数据线;RST主要提供复位功能,其在数据的读写过程中,必须保持为高电位;GND引脚用于和大地相连。

4、内部时钟原理图 (就是一个自激振荡电路) 在内部方式时钟电路中,必须在XTAL1和XTAL2引脚两端跨接石英晶体振荡器和两个微调电容构成振荡电路,通常C1和C2一般取30pF,晶振的频率取值在2MHz~12MHz之间。

5、[数字时钟电路设计图](clock.png)在实现数字时钟电路之前,我们需要先将电路板上的元件焊接好。然后,我们将按照上述步骤连接电路板上的元件。具体而言,我们可以根据以下步骤进行实现:将CD4060集成电路插入电路板上。

6、选择信号源库中的1HZ方波信号作为计数器的测试时钟源。因为秒与分计数均由60进制递增计数器来完成,为在构成数字钟系统时使电路得到简化,我们将图4-1虚线框内建立部分用子电路表示。

什么是源同步

针对普通时钟系统存在着限制时钟频率的弊端,人们设计了一种新的时序系统,称之为源同步时序系统。它最大的优点就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响。

举例说明,某人对学习具有浓厚的兴趣,在课余时间经常到相关网站上查找感兴趣的技术文档,但是,每次都需要打开浏览器去搜索,借助Outlook 2010提供的“RSS源”功能,无需频繁访问网站,即可及时获取自己关注的信息。

这个操作就叫“同步”。同步操作结束之后,两个设备上的数据就完全一致了,处于“同步”状态。一般来讲,两个数据源中,一个是服务器端,一个是客户端。

设置里面的同步,意思解释如下:有两个数据源,最初数据是相同的。

网络性能的优化:移动通信网络中的各个网元之间需要进行协调和配合,以提供高质量的通信服务。如果各个网元之间的时钟不同步,可能会导致网络性能下降,例如通信延迟增加、呼叫质量下降等。

在原理图中怎么接入时钟信号

1、方法如下:两种方法。一种是到网上找看看有没有相应的库。另一种是自己画。AD支持自定义元件。甚至连3D图都能画出来。信号源也称作信号发生器,基本功能是产生并输出期望的信号,可设置信号的频率、功率和调制类型。

2、内部时钟原理图 (就是一个自激振荡电路) 在内部方式时钟电路中,必须在XTAL1和XTAL2引脚两端跨接石英晶体振荡器和两个微调电容构成振荡电路,通常C1和C2一般取30pF,晶振的频率取值在2MHz~12MHz之间。

3、在控制指令字输入后的下一个SCLK时钟的上升沿时,数据被写入DS1302,数据输入从最低有效位即位0开始。同样,在紧跟8位的控制指令字后的下一个SCLK脉冲的下降沿读出DS1302的数据,数据输出时也是从最低有效位即位0开始。

到此,以上就是小编对于的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏