本篇目录:

接片选译码器可以用低位线吗

1、双2-4线译码器转换为3-8线译码器的电路原理图如下:所需要的器件为2片2-4线译码器(74139系列)和1个非门。其中z是最低位。x是最高位。原理如下:当x为0时,上边的译码器打开,下边的译码器输出高阻抗。

2、从上面两个例子看出,译码器虽然简单,但是其用法却多种多样,可以从不同的角度灵活使用译码器完成特定的功能。

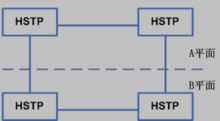

3、结合逻辑地址分段的思路使用两个3-8线译码器的表示对应的Q0~Q7和Q8~Q15。

4、将双2-4译码器进行级联,即使用最高位作为两片2-4译码器的片选信号,将剩余位作为译码器片内地址线,就可以转换成3-8译码器。当x为0时,上边的译码器打开,下边的译码器输出高阻抗。译码输出低4位(yz组合)。

5、这时可以使用译码方式,对单片机剩余的高位地址线进行译码,用译码器的输出线做为单片机芯片的片选。

如何学习zynq以太网控制器及协议栈

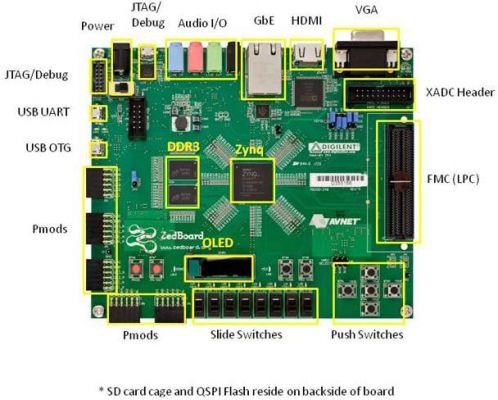

输入 first_zynq_design 作为 Project name, 选择 C:/XUP/Zed 作为 Project location,确保 Create project subdirectory 被勾选上,如图 9-3,点击 Next。

以太网控制器也称以太网适配器,就是我们通常称的“网卡”,其安装方法即是插在机器主板的PCI扩展槽里,一般为白色,然后安装所购买网卡中内附的驱动光盘即可。

图省事的话,笔记本可以去官方网站下载驱动安装,台式机去主板厂商官网下载安装。一般从首页找到技术支持服务,进入驱动档案下载,或者直接搜索相应产品型号。专业的做法,根据硬件ID精确匹配网卡驱动。

高级无线网络知识模块知识点包括:微功耗8011标准WIFI传感器网络原理和结构,内置多ARM和WI-FI收发器的无线单片机,8011 蓝牙技术和低功耗蓝牙无线技术原理;Wi-Fi/蓝牙,ZIGBEE PRO 无线通讯协议栈原理和设计。

以太网控制器:以太网控制器使用一个特定的物理层和数据链路层标准,例如以太网或令牌环来实现通讯所需要的电路系统。

xc9572可以用vivado开发吗

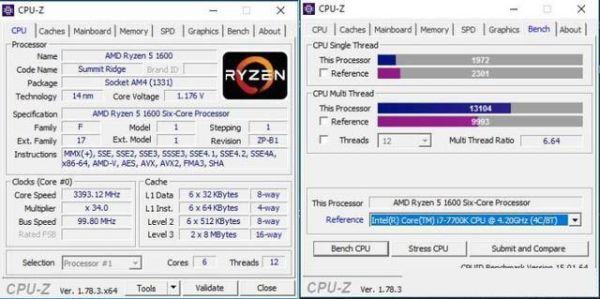

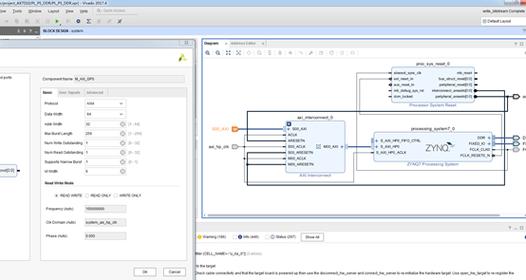

1、对于ZYNQ,掌握PS与PL的高速接口;掌握几种DMA的区别与用法;能够编写基于AXI-4总线的用户IP且打包,意味着对ZYNQ器件的掌握已经进入了真正的入门,或中级水平。

2、常用的可编程逻辑器件的开发环境有很多种,主要有以下几种:CODESYS:这是一种常用的工业自动化控制器开发环境,可以用于可编程逻辑控制器(PLC)和工业PC等设备的开发。

3、不可以,Vivado设计套件,是FPGA厂商赛灵思公司2012年发布的集成设计环境。所以他只能开发塞灵思自己的fpga对于其他家的fpga是不行的。

4、所以针对新的Artix-7/Kintex-7/Virtex-7芯片,Xilinx都建议我们使用全新设计的Vivado套件来进行开发(使用Spartan-6的筒子可以在新设计中考虑向Artix-7过渡了)。

5、Vivado是Xilinx最新的FPGA设计工具,支持7系列以后的FPGA及Zynq 7000的开发。与之前的ISE设计套件相比,Vivado可以说是全新设计的。无论从界面、设置、算法,还是从对使用者思路的要求,都是全新的。

linuxzynq

用于创建BOOT.bin需要的文件(1)u-boot.elf:在Linux下编译后生成u-boot文件,再强制改名为u-boot.elf文件,得到之。(2)zynq_fsbl_0.elf:在EDk下创建得到之。

强大的软件支持:Linux是一种流行的开源操作系统,具有广泛的软件支持和社区支持。使用Linux操作系统可以轻松地访问各种软件和工具,从而提高开发效率。

区别就是ZYNQ除了传统FPGA外,还把ARM核和FPGA结合在了一起,成为了内嵌处理器硬核的FPGA,即SOC FPGA,二者利用高速总线AXI4进行通信。

linux模拟器 qemu,Zynq Linux系统软件模拟器Xilinx/QEMU_遗忘在角落的...Xilinx基于QEMU系统模拟器Xilinx/QEMU可用于模拟运行Zynq Linux的运行与调试。

Linux上的网口eth0、eth1的顺序,似乎是按照phy地址从小到大来排布的。

在前一篇博客中,我们采用xilinx针对Zynq 7000处理器提供的spi-cadence.c驱动实现了芯片上SPI总线驱动的注册,接下来需要修改设备树文件以时我们的外设挂接在SPI总线下。

如何利用Zynq-7000的PL和PS进行交互

vivado2012月份之前的版本,PL要向PS接入多个中断,需要添加一个IP,就是concat这个IP,根据你的中断个数配置这个IP就好了。

第四步:在PL侧网口上验证Jumbo Frame特性,并在应用层适配gigE Vision协议。根据《xapp1082》可知,PL侧的PHY支持1000Base-X和SGMII两种配置,这两种配置对应两种不同的PHY引脚接口(连接到MAC)。

(2)软件的调制解调、信道编码、交织等组件、PL端xilinx官网IP或自搭建IP、软件C语言中的功能函数、PS与PL之间交互的AXI模块;(3)硬件驱动的各类接口芯片驱动。

ZYNQ不光有在.bd里供我们拖拽框图的PL区域的DMA,还有位于PS处理器内的ARM公版DMA硬核,代号为PL330。具体TRM可见下链接(ARM PL330 Technical Reference Manual)。

用于创建BOOT.bin需要的文件 (1)u-boot.elf:在Linux下编译后生成u-boot文件,再强制改名为u-boot.elf文件,得到之。(2)zynq_fsbl_0.elf:在EDk下创建得到之。

实现嵌入式视觉和机器学习基于可编程逻辑的解决方案越来越广泛地用于嵌入式视觉应用,例如异质的赛灵思(Xilinx) All Programmable Zynq-7000 SoC和Zynq UltraScale+MPSoC等多处理器SoC(MPSoC)。

到此,以上就是小编对于zynq pl访问ps ddr的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏