本篇目录:

- 1、芯片电路有几层

- 2、verilog的行为级描述和RTL级描述有什么区别

- 3、verilog里面“**”代表什么?

- 4、简述基于硬件描述语言的数字电路设计流程及其特点。

- 5、数字系统设计高层综合,逻辑综合,版图综合有何区别

芯片电路有几层

芯片虽然个头很小。但是内部结构非常复杂,尤其是其最核心的微型单元——成千上万个晶体管。我们就来为大家详解一下半导体芯片集成电路的内部结构。一般的,我们用从大到小的结构层级来认识集成电路,这样会更好理解。

在一个芯片体内,有大约5级电路,它们共同构成了一个立体的高速公路系统。其中有一些电路层用来铺放晶体管,而另一些则用来连接层并以独特的姿势将单个的晶体管连接起来。

材料介质层在硅晶圆上叠加在一起,就形成了整个芯片上,乃至整个硅晶圆上所有的电路元器件。它们主要包括晶体管(三极管)、存储单元、二极管、电阻、连线、引脚等。

芯片虽然体积小,但内部结构是错综复杂的微电路。通过X射线观看芯片内部结构,可以看到有很多层级,上下交错层叠大概有10层,每一层都有晶体管,通过导线相互连接。在生产的过程中,先完成第一层再向上递进,就和盖楼差不多。

verilog的行为级描述和RTL级描述有什么区别

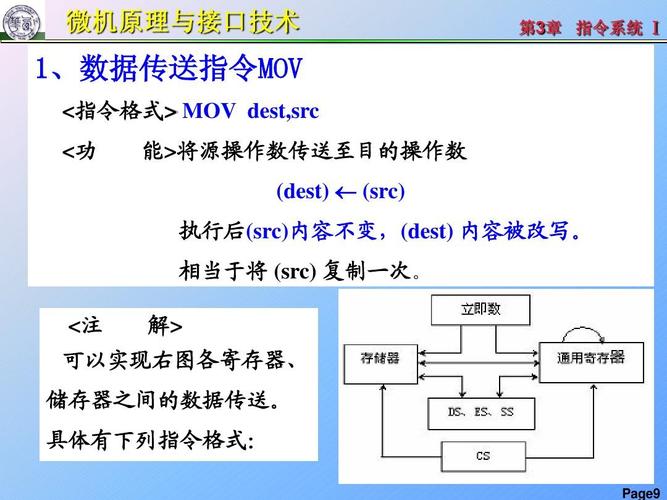

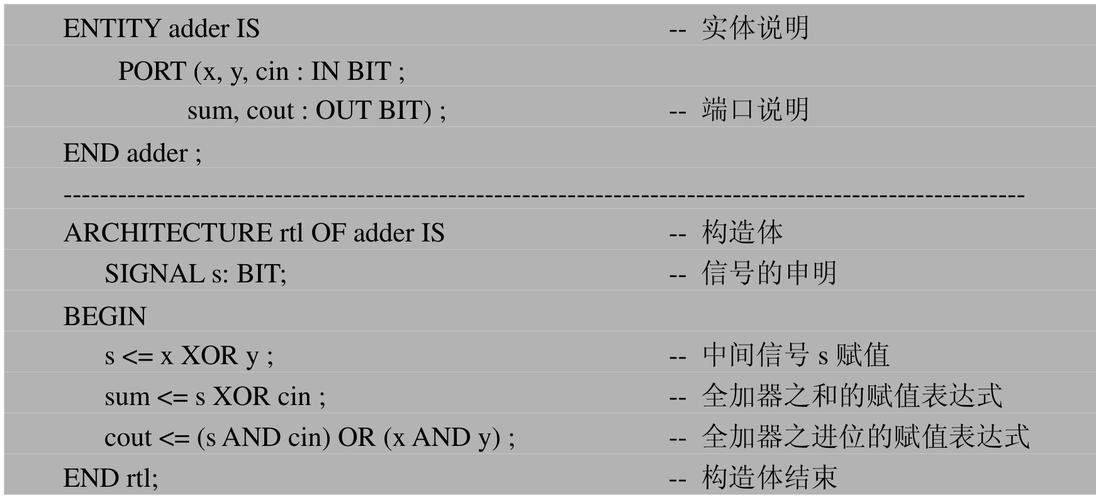

RTL级,register transfer level,指的是用寄存器这一级别的描述方式来描述电路的数据流方式而Behavior级指的是仅仅描述电路的功能而可以采用任何verilog语法的描述方式鉴于这个区别,RTL级描述的目标就是可综合,而行为级描述。

鉴于这个区别,RTL级描述的目标就是可综合,而行为级描述的目标就是实现特定的功能而没有可综合的限制。行为级是RTL的上一层,行为级是最符合人类逻辑思维方式的描述角度,一般基于算法,用C/C++来描述。

Verilog HDL既是一种行为描述的语言也是一种结构描述的语言。这也就是说,既可以用电路的功能描述也可以用元器件和它们之间的连接来建立所设计电路的Verilog HDL模型。Verilog模型可以是实际电路的不同级别的抽象。

RTL级:贴近实际电路结构的描述,描述的细节到寄存器内容传输级别,可以精确描述电路的工作原理、执行顺序,细化到寄存器级别的结构描述也就是RTL级描述。

RTL描述就是用组合电路构成的数据通路+触发器的方式来等效描述原始设计。

verilog里面“**”代表什么?

verilog里面** 表示这是多少次幂。

在Verilog HDL语言有一个特殊的运算符:位拼接运算符{},用这个运算符可以把两个或多个信号的某些位拼接起来进行运算操作。

Verilog是一种硬件描述语言,而always @(*)是Verilog中常用的一种代码结构。它表示在任何输入信号变化时,这一段代码都会触发执行。

是的,这里的*号代替了本always模块里面所有的触发信号。

简述基于硬件描述语言的数字电路设计流程及其特点。

定义电路的功能和结构:根据所需的电路功能,选择合适的硬件描述语言,然后定义电路中的各个模块及其之间的关系。 编写代码:使用选定的硬件描述语言编写代码,描述电路的功能、接口、输入输出等信息。

在方框图一级进行仿真、纠错,并用硬件描述语言对高层次的系统行为进行描述,在系统一级进行验证。然后,用综合优化工具生成具体门电路的网络表,其对应的物理实现级可以是印刷电路板或专用集成电路。

硬件描述语言(HDL):学习硬件描述语言如Verilog、VHDL等,了解如何使用这些语言描述电路的行为和结构,以及如何将HDL代码编译成可编程逻辑器件(FPGA或ASIC)的配置文件。

FPGA的硬件描述语言VHDL,超高速集成电路硬件描述语言,符合美国电气和电子工程师协会标准,利用一种和数字电路基本知识结合较密切的语言来描述数字电路和设计数字电路系统。

在芯片设计阶段.可以使用EDA中的芯片设计工具设计制作芯片的版图。在电路板设计阶段,可以使用EDA中电路板设计工具设计多层电路板。

首先从系统设计入手,在顶层进行功能划分和结构设计,由于采用高级语言描述,能在系统级采用仿真手段验证设计的正确性。

数字系统设计高层综合,逻辑综合,版图综合有何区别

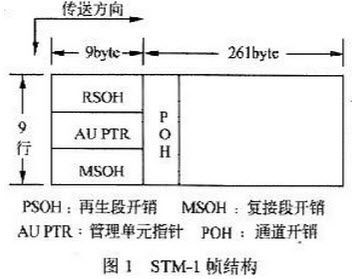

1、【答案】:基于硬件描述语言的数字电路设计包含高层次综合、逻辑综合和物理综合三个阶段的工作。高层次综合也称为行为级综合(Behavioral synthesis),它的任务是将一个设计的行为级描述转换成寄存器传输级的结构描述。

2、(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。(3)从RTL级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。

3、同时确定各子系统之间的接口关系;模块设计是在子系统一级描述电路模块的功能,将子系统划分成更细的逻辑模块;器件设计是将逻辑模块的功能采用通用集成电路或者ASIC来实现;版图设计则包含ASIC芯片版图设计和PCB版图设计。

4、还是综合(版图综合)。所以,综合是将较高层次(抽象)描述转换成较低层次(形象)描述的过程。因为不是所有的高层次描述都可以转换成较低层次地描述的。所以可综合设计,则是指可以转换成较低层次描述的较高层次描述。

5、注意,这种功能仿真没有考虑电路实际的延迟,也无法获得精确的结果。3.逻辑综合确定设计描述正确后,可以使用逻辑综合工具(synthesizer)进行综合。

到此,以上就是小编对于寄存器传递参数的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏