本篇目录:

vpx3u板卡点定义

u是具体尺寸吧,1651*100*26 vpx单板机 VPX资料 VPX主板 VPX SINGLE BOARD COMPUTER 各类板卡的物理尺寸规范 详细描述PCI,PCI-E,CPCI,PC104 板卡知识及其物理尺寸规范。

vpx3u板卡点定义为PCB晶片形式。vpx3u板卡含两片用于信号处理的TI高端C6678 DSP,每片DSP可支持最大4GB的DDR3 SDRAM,板间可以通过SRIO和PCIe进行互联扩展。该板卡主要应用于雷达、电子对抗、软件无线电等领域。

请教FPGA用SRIO通信时Doorbell发送和响应检测的问题

doorbell是消息的一种,需要写功能代码控制实现,不是IP核可以自己完成的。

你在V5里面例化一个SRIO的IPcore,就能和DSP通信了。具体怎么做,根据你的实际情况有相应的设置,建议你还是去看看xilinx的SRIO的UG。还有高速接口物理上serdes信号的调试,涉及硬件,比较麻烦的。

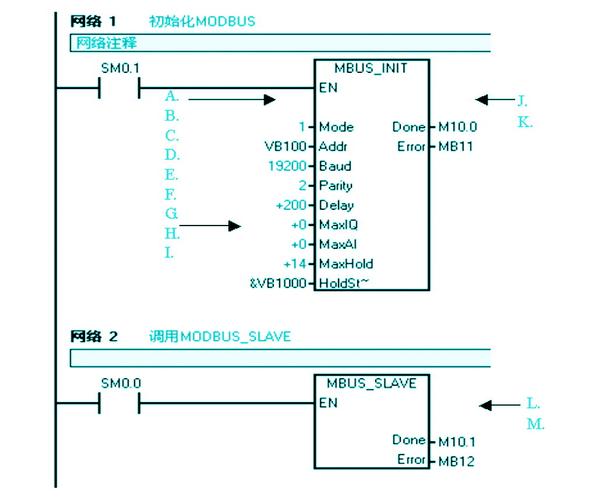

当以帧同步字打头的一帧数据以串行位流的形式到来时,FPGA产生的帧同步脉冲可以直接启动DSP同步串行口接收数据,该同步脉冲同时以中断方式通知DSP为一帧数据的接收做好准备。

doorbell是有响应的,IP核会自动发响应,无响应说明有问题 FPGA收到响应后会在LOG层有包通知你,收到这个包后,要干什么,取决于你自己的需求。

Srio能交叉吗

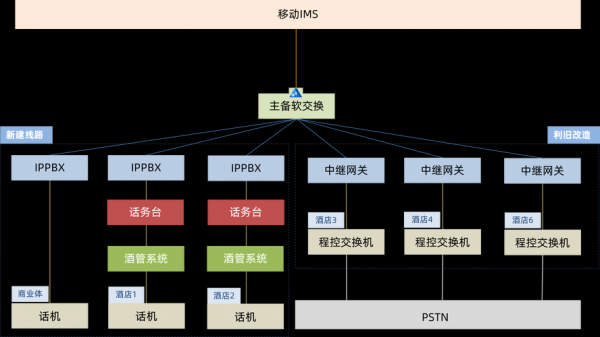

1、RapidIO的互连拓扑结构非常灵活,除了通过交换器件外,两个终端器件也可直接互连。以TI的TMS320C6455DSP为例,它有4个3,125G的SRIO口,可支持的拓扑结构如图4所示。

2、为了确保双偏振信道链路的安全,交叉偏振鉴别率(XPD)因子是通信链路系统避免双偏振信道间干扰的重要因素。大气传播的交叉偏振鉴别率、机载和地面天线的交叉偏振鉴别率是主要因素。因此,我们研发了波纹喇叭天线和隔板偏振器。

3、可以扩大内存,最大是支持4GB,如果XP系统,只能支持到4G左右。楼上两个真会装。2G左右是最佳状态?哥笑了。

4、不能。SRIO可以作为主机的接受端,外部设备可以突发写入DSP,可以不必向CPU产生中断,不依赖与EDMA 数据包的最大值为256字节,每条消息最多16个包,每个包产生一个请求(DMA将数据传到L2)。

串行RapidIO:高性能嵌入式互连技术_高性能嵌入式计算

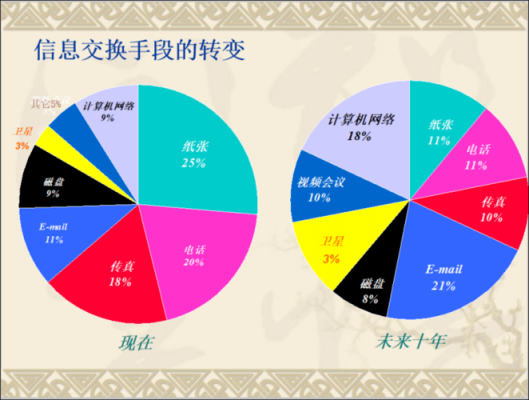

1、表1总结比较了的三种带宽能达到loGb/S的互连技术:以太网、PCIEXpress和串行RapidIO。可以看出串行RapidIO最适合高性能嵌入式系统应用。

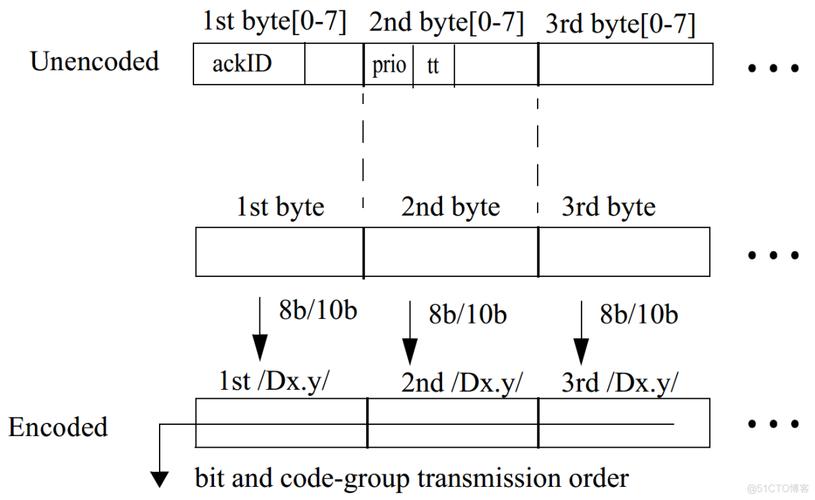

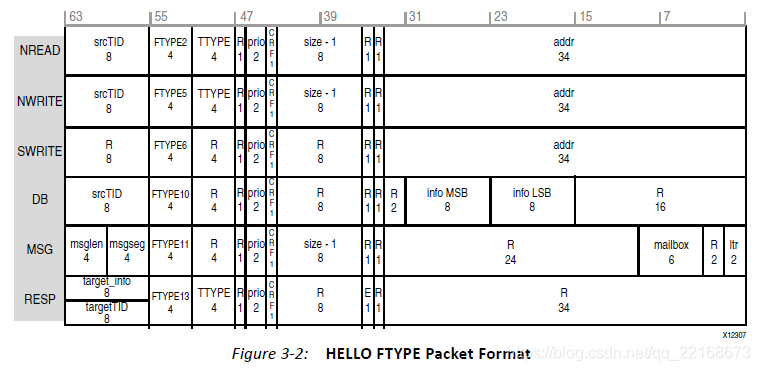

2、RapidIO技术是一种高性能、低引脚数、基于数据包交换交叉开关互连技术,其被定义为三级分层体系结构,分别为逻辑层、传输层和物理层,可以实现从1Gbps到60Gbps通信速率。

3、RapidIO是由Motorola和Mercury等公司率先倡导的一种高性能、 低引脚数、 基于数据包交换的互连体系结构,是为满足和未来高性能嵌入式系统需求而设计的一种开放式互连技术标准。

4、可扩展的处理器结构,以能最迅速地开展出满足应用的最高性能的嵌入式微处理器。 嵌入式微处理器必须功耗很低,尤其是用于便携式的无线及移动的计算和通信设备中靠电池供电的嵌入式系统更是如此,如需要功耗只有mW甚至μW级。

5、,高度的独立性:嵌入式技术的使用,只有通过通信接口和应用系统的独立性连接。2,功能齐全:识别的车牌,车标和颜色的一次性有针对性的与现有系统功能强大。

到此,以上就是小编对于j1939多包传送实例的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏