本篇目录:

- 1、求fpga与单片机并行通信程序

- 2、如何实现FPGA与FPGA相互之间进行通讯和扩展

- 3、fpga网线传输可以在哪显示数据

- 4、FPGA中,我想用一个IO口,在一个时钟周期内,传送8位数据。请问用VHDL语...

求fpga与单片机并行通信程序

1、你可以把FPGA当成RAM,也可以自己规定传输协议。你若将FPGA当成RAM建议你好好看下RAM的时序,只要FPGA内部达到时序要求,就可以模仿RAM的行为,当然RAM是有固定时序要求的。

2、可以在FPGA上编一个串口,就可以和单片机通信了 定义一组IO,一定的时序和单片机以并行方式进行通信(对于单片机来说有点浪费接口资源)FPGA等于一个空白的芯片,什么都没有。你需要什么功能,都是要自己编程实现的。

3、使用8951的外部寻址方式,将单片机的数据总线 部分地址总线和控制总线连接到CPLD 然后再CPLD里根据单片机的外部寻址时序读取数据,这种方式CPLD处理最简单,速度最快。

4、MCU等是属于软件编程,程序是顺序执行,即使像DSP有多级流水线,但是程序总体还是顺序的。FPGA是属于硬件编程,程序是并行执行的,可以有多个进程,同时执行不同的功能。 FPGA实现UART,IIC,SPI。

5、首先,从硬件角度上,只要你P0口接上拉电阻(P0为开漏输出),P0和P2接到FPGA端口上面是行得通的。

6、STM32提供了很多片上通信接口,如SPI,I2C,UART等,还可用IO直接并行传输,这些接口在FPGA上都能够实现。关键看你要通讯的数据量,要求的传输速率,对于串行并行的特殊要求,电路板空间要求等综合考虑,选择通讯方式。

如何实现FPGA与FPGA相互之间进行通讯和扩展

还有就是确定一种通信协议,如I2C,SPI,PCI等等,确定了通信协议,FPGA几乎都能实现。

我现的情况跟你一样 就是用的2层板布的2块贴片的FPGA 你的两片FPGA间通信看的IO资源是否够用 如果够用 就可以直接A给B 或者B给A 如果IO紧张的话可以考虑并串转换或者使用双向IO。

把你的问题说得尽可能具体会有助于问题的解决。

STM32提供了很多片上通信接口,如SPI,I2C,UART等,还可用IO直接并行传输,这些接口在FPGA上都能够实现。关键看你要通讯的数据量,要求的传输速率,对于串行并行的特殊要求,电路板空间要求等综合考虑,选择通讯方式。

接下来第一步就是找起始bit,如果连采3次(或4次)都是0的话,说明找到起始bit了,并且当前采样点大概在这个bit的中间了。那么从现在开始,每过8个时钟,就能采到下一个bit的中间位置。

fpga网线传输可以在哪显示数据

1、有以下步骤。通过FPGA开发板进行采集或处理数据。可以通过串口通信、以太网、USB等方式进行,将处理后的数据传输到电脑上。在电脑上打开数据传输通道和处理软件。

2、串口一端接至FPGA开发板,给板子通电后,用示波器直接测串口线的另一端,如果示波器显示的数据和FPGA发送的数据一致,可以肯定FPGA已经在正常工作了。

3、你只要在DE2上开发好板上以太网的驱动就可以与PC机通过网线(交叉线)或者交换机(平行线)来实现数据传递了。

4、用verilog写AD和显示器的驱动,这种办法是最好的,因为FPGA的nios核不强大,用这种方法做出的示波器的频带能达到很宽。

5、所以需要重新计算IP校验和,UDP校验和,统计数据长度,并将结果封装到数据包中去。最后新收获是,在全双工模式下,以太网帧的数据长度不能超过1500字节,再减去IP首部20字节,udp首部8字节,因此udp数据长度应该小于1472字节。

6、fpga可以通过串口监控软件来按照约定的波特率从低位到高位接收数据并返回,数据接收完毕后,接着接收并比较奇偶校验位是否正确,如果正确则通知后续设备准备接收数据或存入缓存。

FPGA中,我想用一个IO口,在一个时钟周期内,传送8位数据。请问用VHDL语...

你需要将TXclk倍频 8倍 ,然后一个周期传送一位数据,这样子就可以实现了。

在jsp或者html中使用jquery发送ajax请求,这里是获取后台的某个接口。

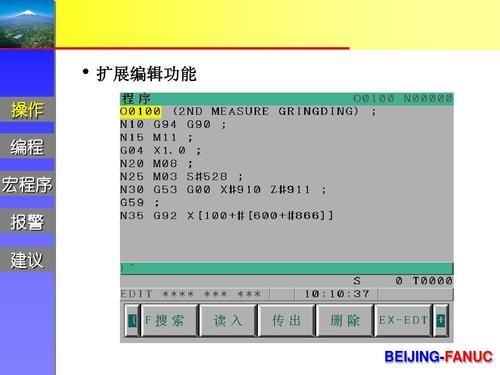

根据RS232 异步串行通信来的帧格式,在FPGA 发送模块中采用的每一帧 格式为:1 位开始位+8 位数据位+1 位奇校验位+1 位停止位,波特率为2400。

到此,以上就是小编对于fpga 并行的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏