本篇目录:

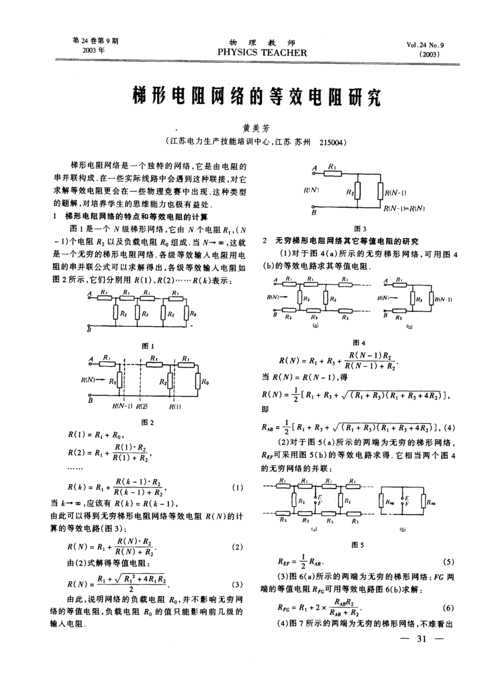

组合电路的分析方法和步骤有哪些?

其一般设计步骤为:① 分析设计要求,列真值表;② 进行逻辑和必要变换。得出所需要的最简逻辑表达式;③ 画逻辑图。

分析设计要求,设置输入和输出变量 列真值表 写出逻辑表达式,并化简 画逻辑电路图 组合逻辑电路的设计方法的例示:有一火灾报警系统,设有烟感、温感和紫外光感3种类型的火灾探测器。

组合逻辑电路的设计步骤一般包括以下几个方面: 确定逻辑功能:根据实际需求,确定电路需要实现的逻辑功能,例如加法、减法、比较、选择等。 确定输入输出:确定电路的输入输出端口,以及输入输出的数据类型和格式。

组合逻辑电路的设计与分析过程相反,其步骤大致如下:(1)根据对电路逻辑功能的要求,列出真值表;(2)由真值表写出逻辑表达式;(3)简化和变换逻辑表达式,从而画出逻辑图。

组合电路的分析步骤大致如下:(1)根据给定的逻辑电路图,写出各输出端的逻辑表达式;(2)对各逻辑表达式进行化简与变换;(3)列出真值表;(4)逻辑功能的评述。

分析步骤:根据给定的逻辑图,从输入到输出逐级写出逻辑函数式;用公式法或卡诺图发化简逻辑函数;3由已化简的输出函数表达式列出真值表;4从逻辑表达式或从真值表概括出组合电路的逻辑功能。

PCB设计实现加法运算怎么做?

要用74LS192制作60进制的加法计算器如下图所示 Proteus软件是英国Lab Center Electronics公司出版的EDA工具软件(该软件中国总代理为广州风标电子技术有限公司)。它不仅具有其它EDA工具软件的仿真功能,还能仿真单片机及外围器件。

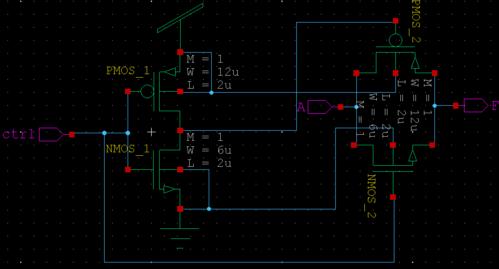

首先得弄清楚全加器的原理,你这里说的应该是设计1位的全加器。全加器有3个输入端:a,b,ci;有2个输出端:s,co.与3-8译码器比较,3-8译码器有3个数据输入端:A,B,C;3个使能端;8个输出端,OUT(0-7)。

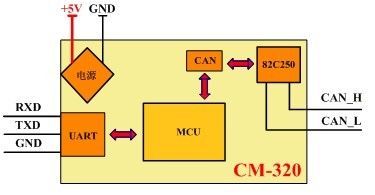

一个数字系统一般由控制部件和运算部件组成,在时脉的驱动下,控制部件控制运算部件完成所要执行的动作。通过模拟数字转换器、数字模拟转换器,数字电路可以和模拟电路互相连接。

自动布局比较方便,但生成的板并不是最优的设计方案,仍然需要手工调整达到预期效果。3布局注意事项 在进行PCB元件布局时,应考虑以下方面。

“工欲善其事,必先利其器”,要做出一块好的板子,除了要设计好原理之外,还要画得好。在进行PCB设计之前,首先要准备好原理图SCH的元件库和PCB的元件库。

每一位的进位信号送给高位作为输入信号,因此,任一位的加法运算必须在低一位的运算完成之后才能进行,这种进位方式成为串行进位,这种加法器的逻辑电路较为简单。

1位十进制加法器的原理

首先得弄清楚全加器的原理,你这里说的应该是设计1位的全加器。全加器有3个输入端:a,b,ci;有2个输出端:s,co.与3-8译码器比较,3-8译码器有3个数据输入端:A,B,C;3个使能端;8个输出端,OUT(0-7)。

加法器原理如下:加法器是数字系统中的基本逻辑器件,减法器和硬件乘法器均可以用加法器来构成。因此,它也常常是数字信号处理系统中的限速元件。

半加器可以将两个位相加,并生成一个进位信号和一个和信号。全加器可以将两个位和一个进位信号相加,并生成一个新的进位信号和一个和信号。多位加法器可以通过连接多个半加器或全加器来实现。

加法器是一种电子计算机中的硬件部件,它能够将两个或多个数字相加并产生一个结果。加法器通常使用二进制进行运算,并使用位运算符(如加号)来执行每一位上的运算。加法器还可能具有进位和溢出检测功能。

该处理用8位的二进制加法器来完成,处理后的数据介于0~99之间,再用同样的方法确定十位Y1即(分别于30、40、50、60、70、80、90比较,为节约时间可用二分法),比较后即可得到十位。

运放加法器原理是什么

它通过将多个输入信号通过次级电压和电流源求和来实现加法。这样,就可以得到一个放大后的输出信号。运算放大器加法器的基本电路结构包括一个运算放大器和多个次级电压和电流源。

经过特殊设计的运放可以允许输入电位在从负电源到正电源的整个区间变化,甚至稍微高于正电源或稍微低于负电源也被允许。这种运放称为轨到轨(rail-to-rail) 输入运算放大器。

运放的基本工作原理是:将输入电压分配到两个内部电阻上,通过改变这两个电阻的电压差来控制输出电压。其中,一个电阻(输入电阻)连接到输入端,另一个电阻(输出电阻)连接到输出端。

运放电路的工作原理如下:两个输入端a(反相输入端),b(同相输入端)和一个输出端o。也分别被称为倒向输入端非倒向输入端和输出端。当电压U-加在a端和公共端(公共端是电压为零的点,它相当于电路中的参考结点。

同相加法器(Adders)是一种电子电路,它可以将两个或多个数字相加。它通常由两个或多个数字输入端和一个输出端组成。在同相加法器中,所有输入信号都具有相同相位(或相对相位)。

总结四位二进制加法器的使用方法

四位二进制数加法器的数据流描述,由于被加数A和加数B都是4位的,而低位来的进位Cin为1位,所以运算的结果可能为5位,用{Cout,Sum}拼接起来表示。

首先,将四个输入位和进位位相加,得到一个中间结果。其次,对于中间结果的每一位,可以用异或门的逻辑电路实现。

可以使用一块四位二进制加法器来实现两个三位二进制数相加。具体实现如下:将两个三位二进制数分别表示为 A 和 B,并且假设 A 的前三个字节为 a1,a2,a3,B 的前三个字节为 b1,b2,b3。

计算本位加法的结果(不考虑进位),将P和G相加得到S,即为该位的和。计算本位加法的进位,将G和上一位的进位C0相加得到C4,即为本位加法的进位。

四位二进制全加器(4-bitbinaryfulladder)是一种电子电路,它可以对四位二进制数(即0~15)进行加法运算。它由三个二位二进制全加器(halfadder)和一个或门组成。

只需从4位二进制并行加法器的输入端AAA2和A1输入8421码;从输入端BBB2和B1输入二进制数0011,进位输入端C0接上“0”,便可从输出端FFF2和F1得到与输入8421码对应的余3码。

到此,以上就是小编对于传输门实现与门的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏