本篇目录:

ESD电路与器件的图书目录

我这有资源 可以看下 ESD物理与器件https://pan.baidu.com/s/1uGe0MScLOugPOczc5H5cvw?pwd=1234提取码:1234 本书系统地介绍了静电放电(ESD)物理理论及器件设计,并给出了大量实例,将ESD理论工程化。

电路(英语:Electrical circuit)或称电子回路,是由电器设备和元器件, 按一定方式连接起来,为电荷流通提供了路径的总体,也叫电子线路或称电气回路,简称网络或回路。

《模拟、数字及电力电子技术(上册)》的目录:编者的话模拟电子篇第一章 基础知识第一节 线性电路常用的定理第二节 半导体二极管及整流电路导电性能介于导体与绝缘体之间材料,我们称之为半导体。

半加器的版图设计详细流程谁知道?急!!!

1、成电路制造技术和工艺流程:双极型工艺(典型TTL?IC制造流程);MOS工艺(典型单阱硅栅CMOS工艺流程和方法);双极型IC和CMOSIC的比较。MOSFET结构、特性、参数、模型。

2、用与非门及用异或门、与门组成的半加器电路如下:与非门是数字电路的一种基本逻辑电路。是与门和非门的叠加,有多个输入和一个输出。 与非门是与门和非门的结合,先进行与运算,再进行非运算。

3、该半加法器采用异或门(74LS86)和双非门、双片74LS00和双非门实现。最基本的逻辑关系是和、或、和,而最基本的逻辑门是和、或门与非门。逻辑门可以由电阻、电容、二极管、三极管等分立元件组成。

4、半减器的设计过程: 列真值表 A B Y 0 0 0 0 1 1 1 0 1 1 1 0 写逻辑表达式 Y=AB+AB 选一个异或门可直接实现。

5、半加器是完成两个1位二进制数相加的组合逻辑电路。所谓半加是指只考虑加数与被加数,不考虑低位进位的加法运算。

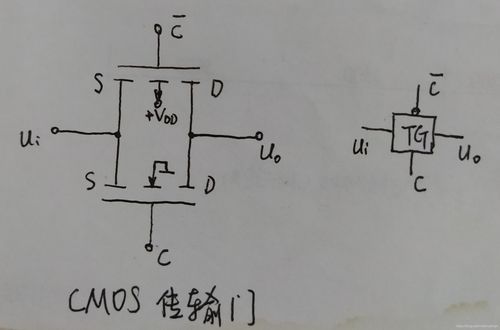

传输门的逻辑功能

1、与非门的逻辑功能是与门和非门的叠加,有多个输入和一个输出。与非门是与门和非门的结合,先进行与运算,再进行非运算。与非运算输入要求有两个,如果输入都用0和1表示的话,那么与运算的结果就是这两个数的乘积。

2、在第二传输门输出端的保持电路能在输入线与输出线断开之后保持锁存器输出端处的逻辑值。

3、CMOS传输门:又称模拟开关 所谓传输门(TG)就是一种传输模拟信号的模拟开关。

专用积体电路设计基础教程详细资料大全

1、本书首先论述了航空专用积体电路相关概念、设计方法等基本理论,内容涉及机载汇流排网路及专用积体电路、面向航空电子系统小型化、单片高密度电路设计与实现方法(主要有ASIC、SoC及MEMS),以及高密度航空电子封装方法(主要是MCM和SiP)。

2、如门电路、多路开关、触发器、时钟发生器等,将它们按照某种特定的规则排列成阵列,做成半导体门阵列母片或基片,然后根据电路功能和要求用掩膜版将所需的逻辑单元连线成所需的专用积体电路。

3、国家专用积体电路系统工程技术研究中心(国家ASIC工程中心)组建于1992年,教育部、江苏省科技厅主管,依托于东南大学。1995年通过国家科技部组织的验收,历次通过国家科技部评估,2000年、2007年分别获国家科技部再建设支持。

为什么说理想的内插是不能物理实现的?

1、理想的 内插 滤波器是非因果的,无法实现。实际的滤波器(一阶保持)需要对理想滤波器进行因果近似,无法对 采样信号 的频率进行理想的过滤。所以无法实现理想的内插。

2、第三代EDA工具对提高ASIC设能力功不可没,为缩短TTM (time to market)发挥了重要作用,但其设计往往不能达到最优。

3、因为非因果性,不符合Paley-Wiener准则,是物理上不可能实现的,但对理论分析很有帮助。理想低通滤波器为一种假想的低通滤波器,其对于高于截止频率的信号完全截止,而对于低于截止频率的信号完全无失真传输。

到此,以上就是小编对于传输门版图设计virtuoso的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏