本篇目录:

64位加法器怎么接

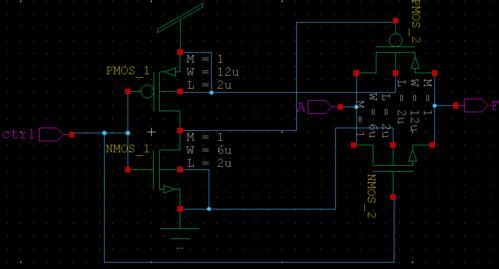

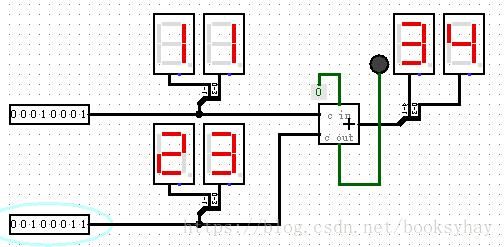

1、其实实现64位加法器,我们的思路是:先实现一位加法器,然后实现4位加法器,由4个4位加法器实现一个16位加法 器,然后由4个16位加法器实现一个64位加法器。

2、ls161改十进制进位端接的方法如下:需要将四个计数输出Q0Q3连接到一组BCD加法器的输入端A0A3,并将CARRY输出连接到BCD加法器的进位输入端CIN。74LS161的Q0Q3输出分别连接到BCD加法器的输入端A0A3。

3、色打印机的9种颜色通常包括:青色、品红色、黄色、黑色、洋红色、浅青色、浅品红色、灰色和白色。

4、泰康人寿的畅赢人生:30岁起一年交5万,交15年,共45万交完钱从第16年开始每年领5万,一直领到99岁,到时候还有一笔钱可以留给下一代,大概有个130万左右。

5、方法如下:准备两个输入信号A和B,以及一个输出信号S。使用两个输入信号A和B连接到一个集成电路(如74LS83或74LS283)的A和B输入端。将输出信号S连接到该集成电路的输出端。

74ls194能否实现十进制加法

LS194是4位双向移位寄存器,利用它只能构成移位型计数器,如环形四进制计数器和扭环形八进制计数器,而不能实现十进制加法计数。

前面的 课程 中讲解了74LS163计数器的功能及应用。74LS163是一个基本的计数器,能完成基本的置数、计数甚至加法等功能。

同步双时钟4位二进制计数器。很简单的。这个有异步置位和异步清零两种功能。因此,你可以有两种做法。一种是利用置位的方式。

LS192十进制加/减计数器,可以在十以内改成其它进制的加/减计数器。用反馈清0法比较简单,五进制计数器,就是当计到五时,输出状态Q3Q2Q1Q0=0101,就利用这个状态产生一个复位信号加到MR端,让计数器回0。

则表示为0。另外设计一个电源电路,将9v的交流电压降到5v,再输入到加法器、减法器电路,能够实现8位的二进制相加或则相减,结果的范围应该在00000000到111111110之间,八位二进制数换算成三位十进制数最大为255。

LS191是4位二进制可逆可预置计数器,用作十进制计数需要加别的电路才能完成,建议改为74LS192,是十进制可逆可预置计数器,管脚功能只有第5脚有一点区别,其它一样。

串行进位加法器原理是什么

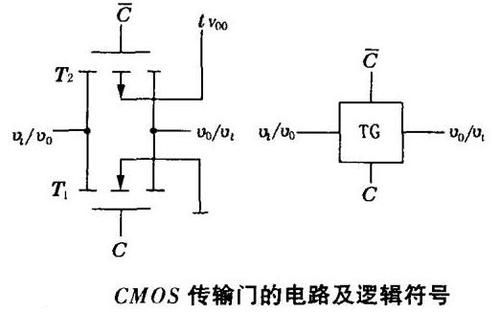

它的工作原理是逐位地将两个数的相应二进制位相加,同时考虑进位。串行加法器通常由多个元件,包括异或门(XOR),与门(AND)和或门(OR)组成。每一位的运算结果会被输出到对应的输出端,并且将进位输出给下一位的计算。

串行进位加法器是将全加器级联构成多位加法器。并行进位加法器通常比串行级联加法器占用更多的资源。随着位数的增加,相同位数的并行加法器与串行加法器之间的差距也越来越大。

加法器的基本原理是,将输入的两个数值的二进制表示形式的对应位相加,如果有进位,则将进位符号传递给下一位。这样,加法器就能够精确地计算出两个数值相加的结果。

全加器可以将两个位和一个进位信号相加,并生成一个新的进位信号和一个和信号。多位加法器可以通过连接多个半加器或全加器来实现。在计算机中,加法器通常由运算器中的加法单元(ALU)实现。

加法器是一种电子计算机中的硬件部件,它能够将两个或多个数字相加并产生一个结果。加法器通常使用二进制进行运算,并使用位运算符(如加号)来执行每一位上的运算。加法器还可能具有进位和溢出检测功能。

加法器原理及电路图如下:二进制加法1个bit的二进制相加,结果将会是2个bit。多出来的那个bit是进位,就像十进制的两个数相加一样。

运放加法器原理是什么

1、它通过将多个输入信号通过次级电压和电流源求和来实现加法。这样,就可以得到一个放大后的输出信号。运算放大器加法器的基本电路结构包括一个运算放大器和多个次级电压和电流源。

2、运放(Operationalamplifier)是一种模拟电子元件,通常被称作运算放大器或简称运放。运放具有很高的放大倍率,并且能够进行各种简单的运算,如加法、减法、乘法和除法等,因此在很多电子系统中被广泛使用。

3、经过特殊设计的运放可以允许输入电位在从负电源到正电源的整个区间变化,甚至稍微高于正电源或稍微低于负电源也被允许。这种运放称为轨到轨(rail-to-rail) 输入运算放大器。

4、运放的基本工作原理是:将输入电压分配到两个内部电阻上,通过改变这两个电阻的电压差来控制输出电压。其中,一个电阻(输入电阻)连接到输入端,另一个电阻(输出电阻)连接到输出端。

5、运放原理运放(OperationalAmplifier)是一种电子电路元件,具有高增益、低输入电阻和高输出电流能力。运放通常用于模拟电路中,作为电压放大器、电流放大器、滤波器、比较器等。运放的基本原理是通过把输入信号放大后再输出。

二位二进制加法器建模原理

原理:74LS74为双D触发器,即带有两个D触发器,令其各为一个计数器,再将其串联即可形成一个加法金属器。

加法器的基本原理是,将输入的两个数值的二进制表示形式的对应位相加,如果有进位,则将进位符号传递给下一位。这样,加法器就能够精确地计算出两个数值相加的结果。

二进制全加器用于门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

) 输入并调出校准信号波形 ,校准信号输出端通过专用电缆与 Y1(或 Y2)输入通道接通,根据实验原理中有关示波器的描述, 正确设置和调节示波器各控制按钮、有关旋钮,将校准信号波形显示在荧光屏上。

只需从4位二进制并行加法器的输入端AAA2和A1输入8421码;从输入端BBB2和B1输入二进制数0011,进位输入端C0接上“0”,便可从输出端FFF2和F1得到与输入8421码对应的余3码。

从而找到一个恰到好处的应用方案。 4位并行加法器之间是并行关系,但是各级全加器之间仍然是级联关系,这是因为FPGA使用查找表的原理实现加法功能,因而可以直接实现并联加法功能,而不需要优化内部CMOS进位链的结构。

实现两个一位二进制数相加的电路叫全加器对吗

1、英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。

2、全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。

3、全加器是能够计算低位进位的二进制加法电路。相加时不考虑进位的二进制加法则称为半加,所用的电路叫做半加器。相加时考虑来自低位的进位以及向高位的进位的二进制加法则称为全加,所用的电路叫做全加器。

4、全加器用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

5、A.两个同位的二进制数相加;B.两个二进制数相加;C.两个同位的二进制数及来自低位的进位三者相加;D.不带进位的两个。答案:C。全加器,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。

6、这是通过将两个数字的每一位分别相加来实现的,并且在需要时进行进位。全加器电路通常由多个半加器单元组成,每个半加器负责处理两个数字的一位。

到此,以上就是小编对于传输门型加法器的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏