本篇目录:

当输出波形和输入波形反相时,导通延迟时间和截止延迟时间分别指什么

通常将从输入波上沿中点到输出波下沿中点的时间延迟称为导通延迟时间t(PHL),从输入波下沿中点到输出波上沿中点的时间延迟称为截止延迟时间t(PLH)。

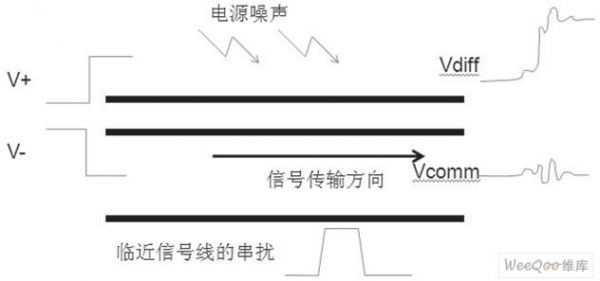

是指系统的输出信号与输入信号,只有幅度的大小与出现的时间先后不同,波形上没有变化称为无失真传输。失真是什么 信号经系统传输,要受到系统函数的加权,输出波形发生了变化,与输入波形不同,则产生失真。

这样在0~0.7就存在死区,不能完全模拟出输入信号波形,PNP型小于-0.7V才导通。比如当输入的交流的正弦波时,在-0.7~0.7之间两个管子都不能导通,输出波形对输入波形来说这就存在失真,即为交越失真。

即存在死区电压Vr。当输入信号电压小于死区电压时,2只晶体管基本上都不导通,这样,当输入信号为正弦波时,输出信号将不再是正弦波,即产生了失真。因此在正、负半周交替过零处会出现一些失真,这个失真称为交越失真。

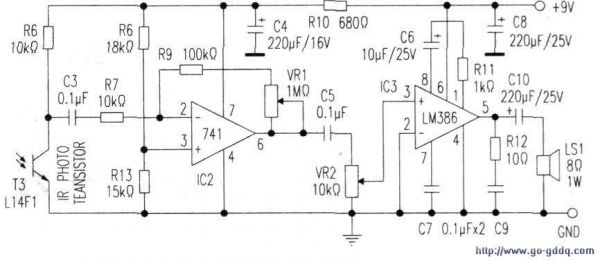

当输入信号为低电平时,Q2截止,Q1导通,IGBT的G极接地,IGBT关断。此时线盘感应电压对谐电容放电,形成了LC振荡。R6电阻在三极管截止时,把IGBT的G极残余电压快速拉低。

门电路的平均传输延迟时间是

平均传输延迟时间t(pd):平均延迟时间是衡量门电路速度的重要指标。TTL与非门的特性参数:输出高电平U(OH):至少有一个输入端接低电平时的输出电平。

又称HTTL系列,该系列的平均传输延迟时间为6ns/门,平均功耗约为22 .5mW/门。3.CT74L低功耗系列 又称LTTL系列,电路的平均功耗约为lmW/门,平均传输延迟约为33ns/门。4.CT74S肖特基系列 又称STTL系列。

CMOS反相器的平均传输延迟时间约为10ns。双极型门电路TTL是transistor-transistorlogic的缩写,就是晶体管到晶体管逻辑电路的意思。COMS是MOS管的,TTL就是晶体管的。

该系列电路主要从制造工艺上作了改进,使其大大提高了工作速度,平均传输延迟时间小于10ns,最高工作频率可达50MHz。HC系列的电源电压范围为2~6V。HCT系列的主要特点是与TTL器件电压兼容,它的电源电压范围为5~5V。

秒。利用六反相器74ls74测量逻辑门电路的时延参数。将74ls74中的六个非门依次串联连接,在输入端输入250KHz的TTL信号,用双踪示波器测总的延时,计算每个门的平均传输延迟时间的tpd的值。

平均延迟时间tpd反映了逻辑门的开关特性,是门电路开关速度的参数,它表示门电路在输入脉冲波形的作用下,其输出波形相对于输入波形延迟了多长的时间。

门电路工作原理?

那么门电路要完成的就是开关动作,举个例子:你发个信号给某个电路,这个电路就让某个灯开了,再发个信号,就关了。

常规门电路,输出依输入出0或1。OC门电路,原理为:集电极开路,使用时要外接上拉电阻,可用于线与。三态门电路,原理为:设有选中控制端端,没被选中的话输出高阻态,相当于未接入线路,用于总线数据传送。

即集电极开路门电路,OD门,即漏极开路门电路,必须外界上拉电阻和电源才能将开关电平作为高低电平用。否则它一般只作为开关大电压和大电流负载,所以又叫做驱动门电路。

集成电路。安全与门实际应用的门电路都是集成电路,由于开放的条件不同,而分为与门、非门、与非门等等,当在规定的位置放入认同的配码钥匙时便可开启门锁、控制门闩,配码有电子配码和物理配码。

逻辑门可以用电阻、电容、二极管、三极管等分立原件构成,成为分立元件门。也可以将门电路的所有器件及连接导线制作在同一块半导体基片上,构成集成逻辑门电路 用以实现基本逻辑运算和复合逻辑运算的单元电路称为门电路。

晶体管门电路的基本工作原理是通过控制门电压来控制电流流动。在NPN晶体管门电路中,当门电压升高时,发射极基极电压会减小,从而使发射极基极电流增加,进而增加发射极源极电流。

到此,以上就是小编对于逻辑门传输延迟时间的测量怎么接线的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏