本篇目录:

FPGA与电脑串口通信verilog程序

小灯亮灭的时间掌握好,用一个计数器来掌握小灯亮灭的时间,不一定要分频。比如说,50MHz的时钟,小灯没1秒变化一次,那么1秒钟走过了50M个时钟,所以把计数器的最大值设置为50M。每次计数器益处,小灯的状态变化。

FPGA的JTGA没有什么设置就可以下进去的,但是AS有三个引脚设置的,如果下载不进去,首先看AS那几个引脚电路是否正确,然后就是看设置是否正确。再就是看你是否生成了相应的AS下载文件。

inout [8:0] data = read_en ? data_read : 8bz;只要让数据总线在读有效的时候等于你模块内部的由地址线决定的要读出的数据,其他时间保持高阻态即可。至于写数据,直接取data值就行了。

本模块的功能是验证实现和PC机进行基本的串口通信的功能。需要在PC机上安装一个串口调试工具来验证程序的功能。

FPGA设计中跨时钟域常见的问题(读书笔记)

从摘要中可以了解到这篇文章主要写了(1)亚稳态现象的出现(2)四种跨时钟域同步方案(3)评估分析(4)优化设计 可以理解为因为有跨时域的设计,在设计中容易出现亚稳态现象,所以要做好跨时钟域同步。

(1)晶振大小根据你的设计而定,十几兆到几十兆不一定,看你的设计要求多少;(2)FPGA往往每个BANK上都有时钟输入,两个晶振应该是连在不同的输入管脚上,可能你的系统要有跨时钟域的问题。

我发现程序资源使用超过75%时就会出现不好使的情况,在逻辑中是否有大量的高字节深度的寄存器或者寄存器组,大的寄存器不利于综合布线,如果会区域约束固化逻辑位置更有利与你解决问题。

FPGA中异步FIFO模块和PLL模块

1、这两个模块之间没有什么必然的联系。需要倍频或者分频时,就用PLL模块;而FIFO常用于在两个传输速率不同的模块之间传输数据的情况。

2、选择要生成模块的程序语言,输入要生成的模块文件的路径和名字。\x0d\x0a第二步进入到类似web的设定参数窗口,可以点击各个步骤的链接跳到相应步骤去。

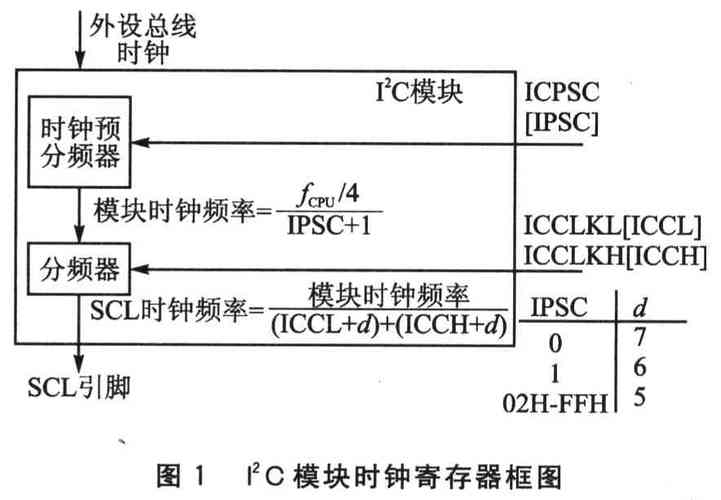

3、DSP利用同步串行口接收FPGA送来的同步串行数据,利用异步串口接收GPS接收机送来时间信息(用于初始化FPGA授时时钟),利用外部总线接口访问FPGA授时时钟、外部SRAM、ISP1581的片内寄存器。

4、一般来说,如果需要满足一定的最大电磁辐射要求和在FPGA上执行高速处理的时候(比如说通信系统中接收器使用的解串器),就需要使用扩频时钟。因此,FPGA中的DCM将乘以输入扩频时钟信号,在内部生成高频时钟信号。

5、FIFO是不会实现数据位数的变换的。它只是实现了数据能被正确的传递。

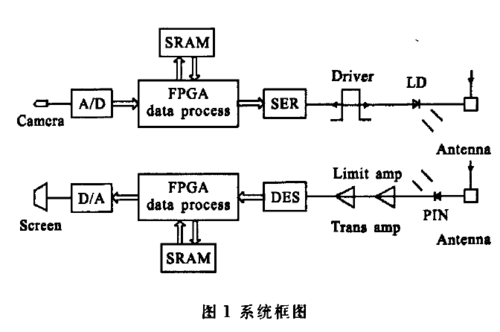

6、其实基于FPGA的高速信号采集几乎都是相同的设计原理。就是先ADC采样信号,将模拟信号转换为数字信号,然后交由FPGA。而此时的FPGA需要写3个IP模块:IP核控制ADC自动高速转换的状态机。

FPGA访问同步SRAM与异步SRAM有什么区别吗

1、同步SRMA比异步SRAM更快。 内存,或内存储器,又称为主存储器,是关系到计算机运行性能高低的关键部件之一,无疑是非常重要的。

2、第一个问题:二者不一样,不是一回事。SRAM型fpga是指,片内的逻辑资源是跟SRAM类似结构的,配置过程就像写ram一样,掉电后消失,结构比SRAM复杂的多,所以每次上电都需要重配置。

3、随机存储器 对于任意一个地址,以相同速度高速地、随机地读出和写入数据的存储器(写入速度和读出速度可以不同)。存储单元的内部结构一般是组成二维方矩阵形式,即一位一个地址的形式(如64k×1位)。

4、与动态RAM相比,静态RAM的集成度较低,并且静态RAM无须考虑保持数据而设置的刷新电路,故扩展电路较简单。由于静态RAM是通过有源电路来保持存储器中的数据,因此,要消耗较多功率,价格也较高。

到此,以上就是小编对于fpga同步和异步的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏