本篇目录:

汇川plc传送指令继存器带z0什么意思?

1、Z0为变址寄存器,Y0Z0是Y(0+Z0),Z0=5的话,Y0Z0=Y5;Y10Z0=Y15。所以你这条指令,是对8个连续的输出赋值,7个赋0,1个赋1,具体Y多少到多少,看Z0,如果Z0=0,则Y7Y6Y5Y4Y3Y2Y1Y0=00000010。

2、举个例子吧, D4Z0就是 D4+Z0里面的数据。

3、Z是变址寄存器,Y0Z0就是是根据Z0的值改变地址,即Y0+Z0的值才是真正输出地址,如Z0=2,那么真正输出的是Y2而不是Y0。LD M8013是秒脉冲,DEC(P)是减一指令,P是上沿触发,也就是说每秒将Z0减去1。

4、Z0为寄存器,不存在点不点亮。当输入MOV K1 Z0时,即可让Z0等于1,当Z0=2时,Y0Z0=Y2,程序为ld m8000、mov d0z0 d20v10。说明:若Z0=2,v10=5,运行指令后,即将D2内面的数据传送到D30。

5、这条指令的意思明白吧-意思就是当x5接通后,就把D100里的值传送给D2。

pcb上的高速信号需要仿真串扰吗

由仿真结果可知,电流流向为反向时的远端串扰峰值(356mm)要大于电流流向为同向时的远端口串扰峰值(260.5)。当干扰源的电流流向改变后,被干扰源的串扰极性也改变了。

避免高频干扰的基本思路是尽量降低高频信号电磁场的干扰,也就是所谓的串扰(Crosstalk)。可用拉大高速信号和模拟信号之间的距离,或加ground guard/shunt traces在模拟信号旁边。还要注意数字地对模拟地的噪声干扰。

如果串扰超过一定的限度就会引起电路的误触发,导致系统无法正常工作。因此了解串扰问 题产生的机理并掌握解决串扰的设计方法,对于工程师来说是相当重要的。

PCB上有高速信号传输,有必要对信号线多加注意;走线与走线之间满足3W规则,减少走线之间串扰;干扰信号不要与敏感信号靠近,尽量隔离;部分信号线设置差分走线,等长处理。

高速系统中,噪声干扰的产生是第一影响因素,高频电路还会产生辐射和冲突,而较快的边缘速率则会产生振铃、反射和串扰。如果不考虑高速信号布局布线的特殊性,设计出的电路板将不能正常工作。

连线要精简,尽可能短,尽量少拐弯,力求线条简单明了,特别是在高频回路中,当然为了达到阻抗匹配而需要进行特殊延长的线就例外了,例如蛇行走线等。

阻抗匹配器的终端控管

当传输线本身的特性阻抗(Z0)被设计者订定为28ohm时,则终端控管的接地的电阻器(Zt)也必须是28ohm,如此才能协助传输线对Z0的保持,使整体得以稳定在28 ohm的设计数值。

对于普通的宽频放大器,输出阻抗50Ω,功率传输电路中需要考虑阻抗匹配,可是如果信号波长远远大于电缆长度,即缆长可以忽略的话,就无须考虑阻抗匹配了。

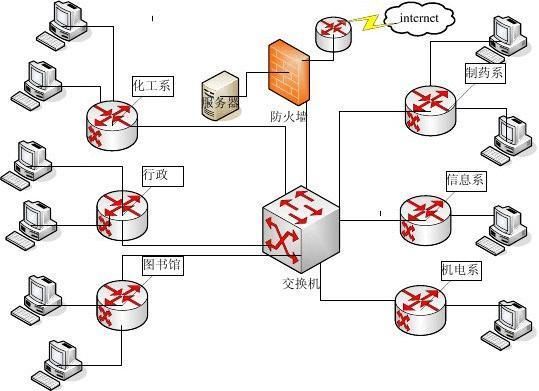

按照网络的拓扑结构,计算机网络可以划分为总线型拓扑、星型拓扑、环型拓扑、树型拓扑、网状拓扑和混合型拓扑。星型拓扑 星型拓扑结构的优点 (1)结构简单,连接方便,管理和维护都相对容易,而且扩展性强。

当传输线本身的特性阻抗(Z0)被设计者订定为28ohm时,则终端控管的接地的电阻器(Zt)也必须是28ohm,如此才能协助传输线对Z0的保持,使整体得以稳定在28 ohm的设计数值。

在有线电视系统中要求使用的同轴电缆特性阻抗为75欧姆。不同的的参数都对应一个最佳的阻抗值。

实际上大多数情况下这种拓扑结构的网络不会是所有计算机真的要连接成物理上的环型,一般情况下,环的两端是通过一个阻抗匹配器来实现环的封闭的,因为在实际组网过程中因地理位置的限制不方便真的做到环的两端物理连接。

请问什么叫阻抗匹配?

1、阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。对于不同特性的电路,匹配条件是不一样的。 在纯电阻电路中,当负载电阻等于激励源内阻时,则输出功率为最大,这种工作状态称为匹配,否则称为失配。

2、阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。对于不同特性的电路,匹配条件是不一样的。

3、阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。阻抗匹配分为低频和高频两种情况讨论。===我们先从直流电压源驱动一个负载入手。

4、时,负载获取电流为0。这两种状态下负载获取的功率都为0,那么介于这两者之间时必然有一个功率最大值。具体的推导过程可参阅相关资料。所以电路最大传输功率的条件是RL=Ro,这个时候也称最佳阻抗匹配,匹配系数为1。

5、这个问题比较含糊。只能从阻抗匹配的原理着手来解释。 考虑纯电阻电路,对专于任何一属个电源来说都存在着内阻,也就是说,电源可以等效成一个恒压源和一个电源内阻的串联电路。

6、在交流信号传输中,要求信号源内阻和负载电阻相匹配,才能使传输功率最大,即两者之比为 也就是说共轭,为使两者之间达到阻抗匹配,实现功率最大传输,要用变压器进行阻抗匹配,才能使负载得到最大传输功率。

...而且走线也不能和IC的PIN脚垂直?会影响到什么

1、的影响呢?从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。其实不光是直角走线,顿角,锐角走线都可能会造成阻抗变化的情况。

2、应该说这样的要求没有道理,如何走线,是根据方便简洁有利于:以最短的路径达到连接,线与线间尽量有较宽的间隙,避免间隙过小,布线过密,拥挤、造成短路,另外凡是涉及电源的布线,尽可能粗一些。

3、走线也不和IC的PIN脚垂直是为了避免集成块引脚触碰走线,对需要连接的走线也是允许的。

4、所有IC电源/地间的电容走线尽量短,并不要使用过孔。 晶振电路 1 所有连到晶振输入/输出端(如XTLI、XTLO)的走线尽量短,以减少噪声干扰及分布电容对Crystal的影响。XTLO走线尽量短,且弯转角度不小於45度。

5、在布线时,如果实在布不过去了,也可以加一个0欧的电阻。在高频讯号下,充当电感或电容。(与外部电路特性有关)电感用,主要是解决EMC问题。如地与地,电源和IC Pin间。

到此,以上就是小编对于传输线的s参数的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏