本篇目录:

- 1、TTL电路和CMOS电路的区别和联系

- 2、电路输出低电平电流和输出低电平漏电流有区别吗?

- 3、TTL电路与COMS电路有什么不同,各有什么特点?

- 4、数字电路中,电路延迟与输入个数(扇入)有关系吗?是不是输入越多延迟越...

TTL电路和CMOS电路的区别和联系

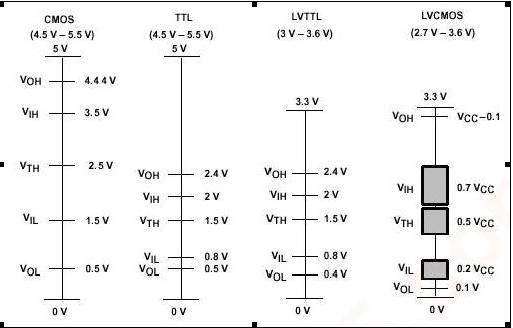

高噪声容限—CMOS电路的噪声容限一般在 40%电源电压以上。宽工作电压范围—CMOS电路的电源电压一般为 5~18 伏。高逻辑摆幅—CMOS电路输出高、低电平的幅度达到全电为VDD,逻辑“0”为VSS。

高低电平不同。TTL高电平6~5V,低电平0V~4V,CMOS电平Vcc可达到12V 。电路输出电平不同。CMOS电路输出高电平约为0.9Vcc,而输出低电平约为 0.1Vcc。电路不使用的输入端不同。

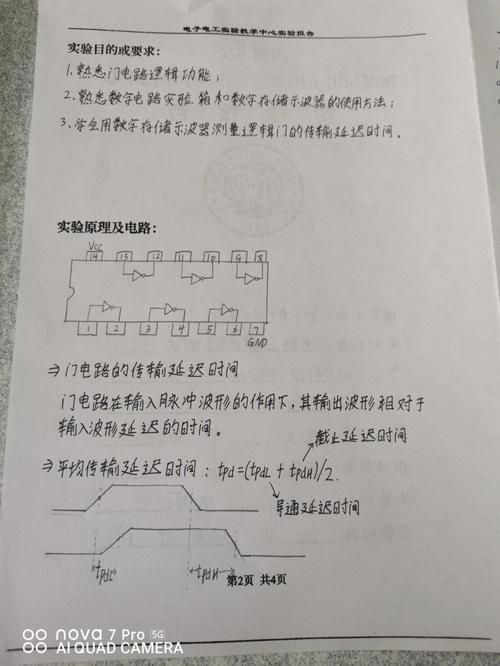

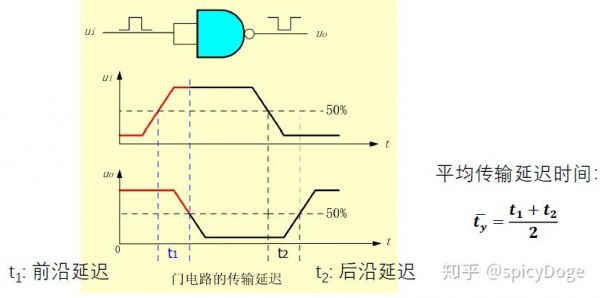

TTL电路是:电流控制器件,CMOS电路:是电压控制器件。传输速度不同:TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。CMOS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。

其次是关于TTL电平和CMOS电平电路的区别。TTL电平和CMOS电平受控制的因素就不一样,TTL电平是受电流控制的器件,而CMOS电平是受电压控制的器件,也正因为如此,两者在传输速度和功耗方面差别也很大。

与TTL门电路的情况不同,影响CMOS电路工作速度的主要因素在于电路的外部,即负载电容CL。CL是主要影响器件工作速度的原因。由CL所决定的影响CMOS门的传输延时约为几十纳秒。

电路输出低电平电流和输出低电平漏电流有区别吗?

1、源型和漏型的含义 源型输入与漏型输入,都是相对于PLC输入公共端(COM端或M端)而言,电流流入则为漏型,电流流出则为源型。

2、由于数字电路的输出只有高、低(0,1)两种电平值,高电平输出时,一般是输出端对负载提供电流,其提供电流的数值叫“拉电流”;低电平输出时,一般是输出端要吸收负载的电流,其吸收电流的数值叫“灌(入)电流”。

3、:输出低电平(Vol):保证逻辑门的输出为低电平时的输出电平的最大值,逻辑门的输出为低电平时的电平值都必须小于此Vol。5:阀值电平(Vt): 数字电路芯片都存在一个阈值电平,就是电路刚刚勉强能翻转动作时的电平。

4、数字电路中,把电压的高低用逻辑电平来表示。逻辑电平包括高电平和低电平这两种。不同的元器件形成的数字电路,电压对应的逻辑电平也不同。

5、理想的数字电路电平是这样的:输入小于1/2VCC(电源电压)就是低电平,反之是高电平。实际的器件是做不到的,也不实用,如果输入电压在1/2VCC附近有干扰,就会发生错误的输入信号。

TTL电路与COMS电路有什么不同,各有什么特点?

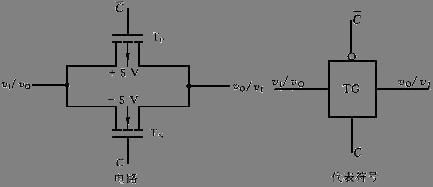

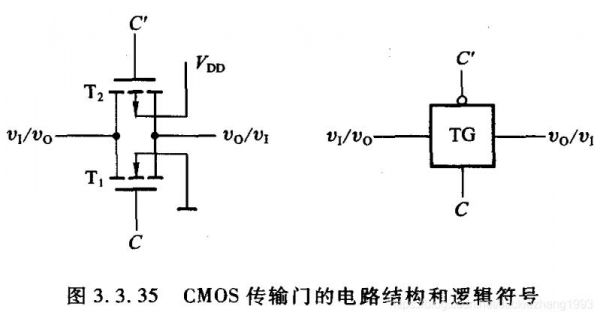

V。 TTL电路是电流控制器件,TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。CMOS(Complementary Metal Oxide Semiconductor),互补金属氧化物半导体,电压控制的一种放大器件。是组成CMOS数字集成电路的基本单元。

高低电平不同。TTL高电平6~5V,低电平0V~4V,CMOS电平Vcc可达到12V 。电路输出电平不同。CMOS电路输出高电平约为0.9Vcc,而输出低电平约为 0.1Vcc。电路不使用的输入端不同。

电路作用不同:TTL电路是:电流控制器件,CMOS电路:是电压控制器件。传输速度不同:TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。CMOS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。

TTL是电流控制器件,CMOS是电压控制器件。TTL的电源工作电压一般为5V。CMOS器件电源工作电压范围宽,有2V ~6V,3V ~18V等,使用就看应用的场合了。

最后,噪声特性方面,TTL电路比CMOS电路更敏感。TTL电路的噪声容限较小,这意味着它们对电源电压的变化和负载变化非常敏感。相比之下,CMOS电路的噪声容限较大,因此它们在嘈杂的环境中表现更好。

数字电路中,电路延迟与输入个数(扇入)有关系吗?是不是输入越多延迟越...

在低频( 1MHz)的工作条件下,CMOS电路的扇出数可以达到50以上。因此。扇入越大越好,扇出越大越坏。在设计中,尽量减小扇出。

扇出(fan-out)是定义单个逻辑门能够驱动的数字信号输入最大量的术语。大多数TTL逻辑门能够为10个其他数字门或驱动器提供信号。因而,一个典型的TTL逻辑门有10个扇出信号。

扇入(fan-in)是定义单个逻辑门能够接受的数字信号输入最大量的术语。大多数TTL逻辑门有一个或两个输入端,也有一些有两个以上的输入端。一个典型的逻辑门有2个扇入信号。

到此,以上就是小编对于晶体管传输延迟时间的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏